이 게시물에서는 4 시간에서 40 시간까지 2 개의 정확한 장시간 타이머 회로를 만드는 방법을 배웁니다.이 회로는 더 긴 지연을 위해 추가로 업그레이드 할 수 있습니다. 개념은 완전히 조정 가능 .

전자 장치의 타이머는 기본적으로 연결된 부하를 전환하기위한 시간 지연 간격을 생성하는 데 사용되는 장치입니다. 시간 지연은 요구 사항에 따라 사용자가 외부에서 설정합니다.

소개

단일 4060 IC 또는 CMOS IC만으로는 길고 정확한 지연을 생성 할 수 없습니다.

4 시간이 지나면 IC 4060이 정확도 범위에서 벗어나기 시작한다는 사실을 실제로 확인했습니다.

지연 타이머로 IC 555는 더 나쁘기 때문에이 IC에서 한 시간 동안도 정확한 지연을 얻는 것은 거의 불가능합니다.

이 부정확성은 주로 커패시터 누설 전류와 커패시터의 비효율적 인 방전 때문입니다.

4060, IC 555 등과 같은 IC는 기본적으로 수 Hz에서 수 Hz까지 조정 가능한 진동을 생성합니다.

이러한 IC가 다음과 같은 다른 분배기 카운터 장치와 통합되지 않는 한 IC 4017 , 매우 정확한 시간 간격을 얻는 것은 불가능할 수 있습니다. 24 시간 또는 요일 및 주 간격은 아래와 같이 디바이더 / 카운터 스테이지를 통합하게됩니다.

첫 번째 회로에서는 효과적인 장기 타이머 회로를 형성하기 위해 두 가지 다른 IC 모드를 함께 결합하는 방법을 봅니다.

1) 회로 설명

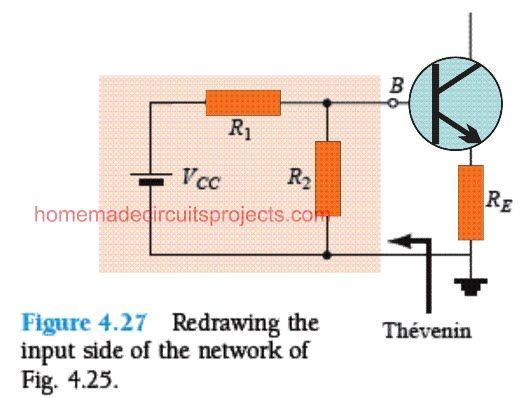

회로도를 참조하십시오.

- IC1은 발진기 단계가 내장 된 발진기 카운터 IC이며 핀 1,2,3,4,5,6,7,9,13,14,15에서 다양한 주기로 클록 펄스를 생성합니다.

- 핀 3의 출력은 가장 긴 시간 간격을 생성하므로 다음 단계에 공급하기 위해이 출력을 선택합니다.

- 포트 P1과 IC1의 커패시터 C1은 핀 3에서 시간 범위를 조정하는 데 사용할 수 있습니다.

- 위 구성 요소의 설정이 높을수록 핀 # 3의 기간이 길어집니다.

- 다음 단계는 IC1에서 얻은 시간 간격을 10 배로 늘리는 것 외에는 아무것도하지 않는 10 진 카운터 IC 4017로 구성됩니다. IC1의 핀 # 3에서 생성 된 시간 간격이 10 시간이면 IC2의 핀 # 11에서 생성 된 시간은 10 * 10 = 100 시간이됩니다.

- 마찬가지로 IC1의 핀 # 3에서 생성 된 시간이 6 분이면 60 분 또는 1 시간 후에 IC1의 핀 # 11에서 높은 출력을 의미합니다.

- 전원이 켜지면 커패시터 C2는 두 IC의 리셋 핀이 적절하게 리셋되도록하여 IC가 관련없는 중간 수치가 아닌 0부터 계산을 시작합니다.

- 카운팅이 진행되는 동안 IC2의 핀 # 11은 로직 로우 상태로 유지되어 릴레이 드라이버가 스위치 OFF 상태로 유지됩니다.

- 설정된 타이밍이 지나면 IC2의 11 번 핀이 하이가되어 트랜지스터 / 릴레이 단계와 릴레이 접점과 연결된 후속 부하를 활성화합니다.

- 다이오드 D1은 IC2의 핀 # 11의 출력이 핀 # 11에서 피드백 래치 신호를 제공하여 IC1의 카운팅을 잠그도록합니다.

따라서 전체 타이머는 타이머가 꺼질 때까지 래치되고 전체 프로세스를 반복하기 위해 다시 시작됩니다.

부품 목록

R1, R3 = 1M

R2, R4 = 12K,

C1, C2 = 1uF / 25V,

D1, D2 = 1N4007,

IC1 = 4060,

IC2 = 4017,

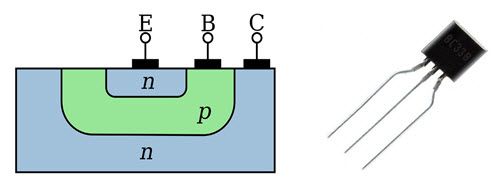

T1 = BC547,

POT = 1M 선형

릴레이 = 12V SPDT

PCB 레이아웃

IC 4060의 지연 출력 계산 공식

지연 기간 = 2.2 Rt.Ct.2 (N -1)

주파수 = 1/2 Rt. Ct

Rt = P1 + R2

Ct = C1

R1 = 10 (P1 + R2)

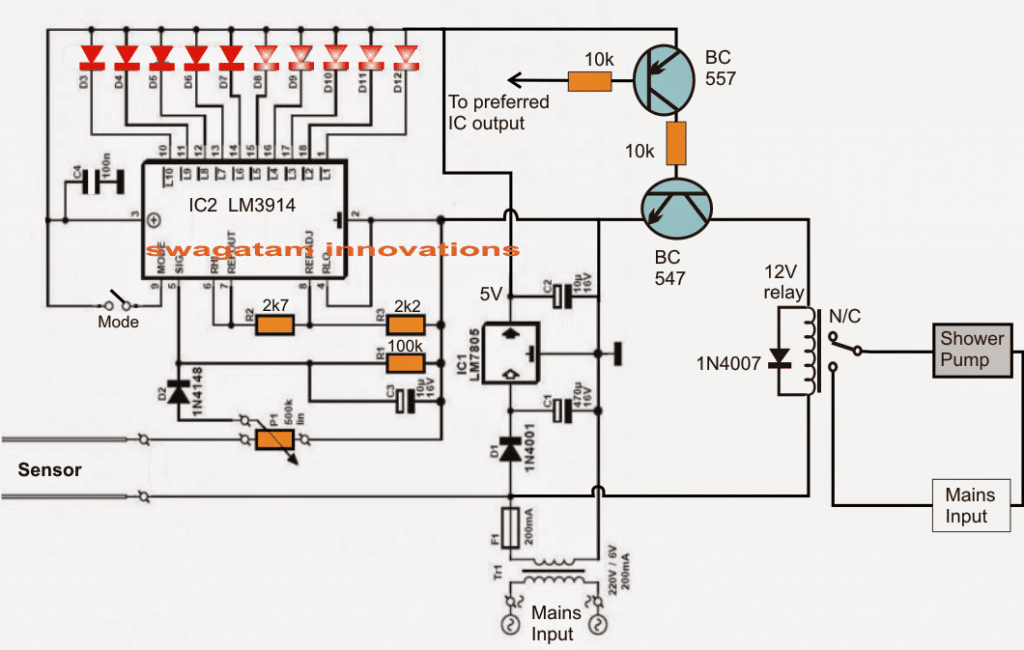

선택기 스위치 및 LED 추가

위의 디자인은 다음 다이어그램에 표시된 것처럼 선택기 스위치와 순차 LED로 더욱 향상 될 수 있습니다.

작동 원리

타이밍 회로의 주요 요소는 4060 CMOS 장치로, 발진기와 14 단 분배기로 구성됩니다.

발진기의 주파수는 전위차계 P1을 통해 조정되어 Q13의 출력이 매 시간마다 단일 펄스가되도록 할 수 있습니다.

이 클럭 비트의주기는 다이오드 D8을 통해 전체 4060 IC를 추가로 재설정하므로 매우 빠를 수 있습니다 (약 100ns).

2 번째 (10 분할) 카운터 인 4017 IC에 '1 시간에 한 번'클럭 펄스가 제공됩니다. 이 카운터의 여러 출력 중 하나는 주어진 순간에 로직 하이 (논리 출력)가 될 것입니다.

4017이 재설정되면 출력 Q0이 높아집니다. 1 시간 후 출력 Q0이 낮아지고 출력 Q1이 높아질 수 있습니다. 결과적으로 스위치 S1은 사용자가 1 ~ 6 시간 동안 시간 간격을 선택할 수 있도록합니다.

선택한 출력이 높아지면 트랜지스터가 꺼지고 릴레이가 꺼집니다 (따라서 연결된 부하가 꺼집니다).

4017의 인 에이블 입력이 S1의 와이퍼에 추가로 연결되면 후속 클럭 펄스가 카운터에 영향을 미치지 않는 것으로 판명됩니다. 결과적으로 장치는 사용자가 리셋 스위치를 누를 때까지 계속 꺼진 상태로 유지됩니다.

7 개의 LED와 함께 4050 CMOS 버퍼 IC가 통합되어 기본적으로 경과했을 수있는 시간 범위를 표시합니다. 이러한 부품은 경과 시간 표시가 필요하지 않은 경우 제거 할 수 있습니다.

이 회로의 소스 전압은 실제로 중요하지 않으며 5V 및 15V 범위를 포함 할 수 있습니다. 릴레이를 제외한 회로의 전류 사용량은 15mA 범위에 있습니다.

문제를 방지하기 위해 릴레이 사양과 일치 할 수있는 소스 전압을 선택하는 것이 좋습니다. BC 557 트랜지스터는 70mA의 전류를 처리 할 수 있으므로 릴레이 코일 전압이이 전류 범위와 정격인지 확인하십시오.

2) BJT 만 사용

다음 설계는 의도 된 동작을 위해 몇 개의 트랜지스터 만 사용하는 매우 긴 기간의 타이머 회로를 설명합니다.

장시간 지연을 실행하려면 IC를 사용해야 만 가능한 높은 정밀도와 정확도가 필요하기 때문에 장시간 타이머 회로에는 일반적으로 IC가 포함됩니다.

높은 정확도 지연 달성

우리 자신의 IC 555조차도 장기간 지연이 예상되면 무력하고 부정확 해집니다.

만난 높은 정확도를 오래 유지하기가 어렵습니다. 지속 기본적으로 누설 전압 문제와 커패시터의 불일치 방전으로 인해 타이머의 시작 임계 값이 잘못되어 각 사이클의 타이밍에 오류가 발생합니다.

누설 및 일관되지 않은 방전 문제는 커패시터 값이 커질수록 비례 적으로 커지고 이는 긴 간격을 확보하는 데 필수적입니다.

따라서 일반 BJT로 장시간 타이머를 만드는 것은 이러한 장치만으로는 너무 기본적 일 수 있고 복잡한 구현에서는 기대할 수 없기 때문에 거의 불가능할 수 있습니다.

그렇다면 트랜지스터 회로는 어떻게 길고 정확한 지속 시간 간격을 생성 할 수 있습니까?

다음 트랜지스터 회로는 위에서 논의 된 문제를 확실하게 처리하고 상당히 높은 정확도 (+/- 2 %)로 장기간 타이밍을 획득하는 데 사용할 수 있습니다.

이는 단순히 새로운 사이클마다 커패시터가 효과적으로 방전되기 때문입니다. 이는 회로가 0에서 시작하도록 보장하고 선택한 RC 네트워크에 대해 정확한 동일한 시간주기를 가능하게합니다.

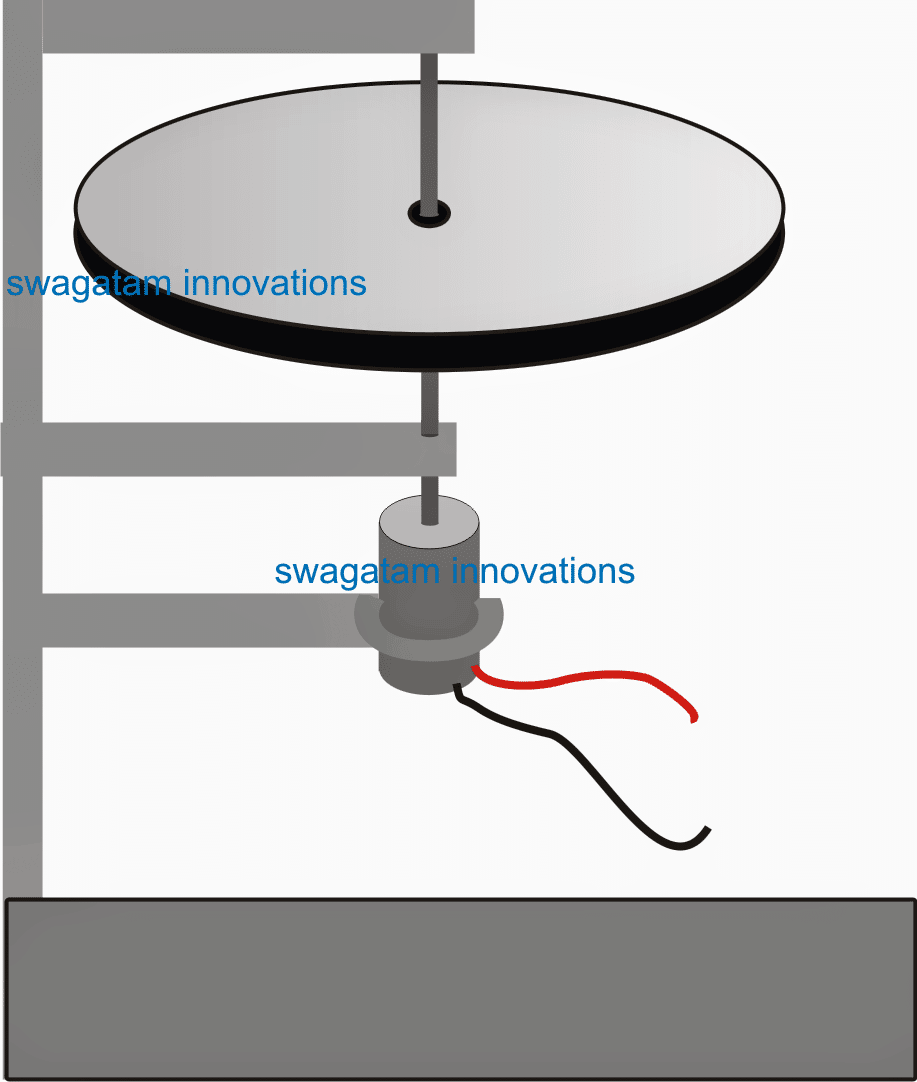

회로도

회로는 다음 토론을 통해 이해할 수 있습니다.

작동 원리

누름 버튼을 잠시 누르면 1000uF 커패시터가 완전히 충전되고 NPN BC547 트랜지스터가 트리거되어 2M2 저항과 NPN의 에미 터를 통한 1000uF의 느린 방전으로 인해 스위치가 해제 된 후에도 위치를 유지합니다.

BC547을 트리거하면 PNP BC557이 켜지고 릴레이와 연결된 부하가 켜집니다.

위의 상황은 1000uF가 두 트랜지스터의 차단 레벨 아래로 방전되지 않는 한 유지됩니다.

위에서 설명한 작업은 매우 기본적이며 성능에 너무 부정확 할 수있는 일반적인 타이머 구성을 만듭니다.

1K 및 1N4148의 작동 방식

그러나 1K / 1N4148 네트워크를 추가하면 다음과 같은 이유로 회로가 매우 정확한 장기 타이머로 즉시 변환됩니다.

1K 및 1N4148 링크는 커패시터의 충전 부족으로 인해 트랜지스터가 래치를 끊을 때마다 커패시터 내부의 잔류 전하가 릴레이 코일을 통해 위의 저항 / 다이오드 링크를 통해 완전히 방전되도록합니다.

위의 기능은 커패시터가 완전히 드레인되고 다음 사이클 동안 비워 지도록하여 0에서 깨끗한 시작을 생성 할 수 있습니다.

위의 기능이 없으면 커패시터는 완전히 방전 될 수 없으며 내부의 잔류 전하가 정의되지 않은 시작점을 유도하여 절차가 부정확하고 일관성이 없게됩니다.

NPN에 대해 Darlington 쌍을 사용하여 회로를 더욱 향상시킬 수 있으므로 기본 및 비례 적으로 낮은 값 커패시터에서 훨씬 더 높은 값의 저항을 사용할 수 있습니다. 값이 낮은 커패시터는 누설을 낮추고 장기간 계수 기간 동안 타이밍 정확도를 향상시키는 데 도움이됩니다.

원하는 긴 지연에 대한 구성 요소 값을 계산하는 방법 :

Vc = Vs (1-e-t / RC)

어디:

- 유커패시터 양단의 전압

- 대공급 전압

- 티공급 전압을 적용한 후 경과 된 시간

- RC이다 시간 상수 RC 충전 회로의

PCB 설계

연산 증폭기를 사용하는 장시간 타이머

모든 아날로그 타이머 (모노 스터 블 회로)의 단점은 상당히 긴 시간을 달성하기 위해 RC 시간 상수가 그에 따라 상당해야한다는 것입니다.

이것은 필연적으로 1M보다 큰 저항 값을 의미하며, 이는 회로 내의 표유 누설 저항 또는 상당한 전해 커패시터로 인한 타이밍 오류를 초래할 수 있으며, 누설 저항으로 인해 유사하게 타이밍 문제를 일으킬 수 있습니다.

위에 표시된 연산 증폭기 타이머 회로는 일반 회로를 사용하여 액세스 할 수있는 시간에 비해 100 배 더 많은 시간주기를 수행합니다.

이는 100 배까지 커패시터 충전 전류를 낮추어 높은 값의 충전 커패시터를 사용하지 않고도 충전 시간을 획기적으로 개선함으로써 달성됩니다. 회로는 다음과 같은 방식으로 작동합니다.

시작 / 리셋 버튼을 클릭하면 C1이 방전되어 전압 팔로워로 구성된 연산 증폭기 IC1의 출력이 0V가됩니다. 비교기 IC2의 반전 입력은 비 반전 입력보다 감소 된 전압 레벨에 있으므로 IC2의 출력은 높게 이동합니다.

R4 주변의 전압은 약 120mV이며, 이는 C1이 R2를 통해 약 120nA의 전류로 충전됨을 의미하며, 이는 R2가 양의 전원에 직접 연결되었을 때 얻을 수있는 것보다 100 배 더 적다는 것을 의미합니다.

말할 필요도없이 C1이 일관된 120mV를 통해 충전 되었다면이 전압을 빠르게 달성 할 수 있고 더 이상 충전을 중지 할 수 있습니다.

그러나 R4의 하단 단자가 IC1의 출력으로 피드백되면 C1 양단의 전압이 상승함에 따라 출력 전압과 R2에 제공되는 충전 전압도 상승합니다.

출력 전압이 약 7.5V로 상승하면 R6 및 R7에 의해 IC2의 비 반전 입력에서 참조 된 전압을 초과하고 IC2의 출력이 낮아집니다.

R8에서 제공하는 소량의 포지티브 피드백은 일반적으로 잘못된 출력 펄스를 생성하기 때문에 IC1의 출력에 존재하는 모든 종류의 노이즈가 IC2에 의해 부스트되는 것을 방지합니다. 타이밍 길이는 다음 방정식으로 계산할 수 있습니다.

T = R2 C1 (1 + R5 / R4 + R5 / R2) x C2 x (1 + R7 / R6)

다소 복잡해 보일 수 있지만 부품 번호가 표시된대로 시간 간격을 100 C1까지 설정할 수 있습니다. 여기서 C1은 마이크로 패럿 단위입니다. C1이 1µ로 선택되면 출력 시간 간격은 100 초가됩니다.

R2를 1M 전위차계로 대체하거나 R6 및 R7 대신 10k pot을 사용하여 대수적으로 타이밍 간격을 선형으로 변경할 수 있다는 것이 방정식에서 매우 분명합니다.

Previous : 전원 공급 장치에이 단락 보호 회로 추가 Next : NAND 게이트를 사용하는 불안정한 멀티 바이브레이터 회로