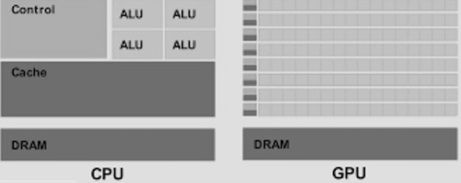

다양한 유형의 디지털 시스템은 AND 게이트, NAND 게이트, 또는 게이트 등과 같은 매우 적은 유형의 기본 네트워크 구성으로 구성됩니다. 이러한 기본 회로는 다양한 토폴로지 조합에서 반복적으로 사용됩니다. 논리를 수행하는 것 외에도 디지털 시스템은 이진수도 저장해야합니다. 이러한 메모리 셀의 경우 FLIP-FLOP ' s가 설계되었습니다. 이진 추가와 같은 일부 기능을 수행합니다. 따라서 이러한 기능을 수행하려면 논리 게이트 FLIP-FLOP은 단일 칩 IC를 통해 설계되었습니다. 이러한 IC는 디지털 시스템의 실용적인 빌딩 블록을 형성합니다. 이진 추가에 사용되는 이러한 빌딩 블록 중 하나는 Carry Look-ahead Adder입니다.

Carry Look-ahead Adder 란 무엇입니까?

디지털 컴퓨터에는 더하기, 빼기, 곱하기 및 나누기와 같은 산술 연산을 수행 할 수있는 회로가 있어야합니다. 이 중 덧셈과 뺄셈이 기본 연산이고 곱셈과 나눗셈은 각각 반복되는 덧셈과 뺄셈입니다.

이러한 작업을 수행하기 위해 'Adder circuits'는 기본 로직 게이트를 사용하여 구현됩니다. 가산기 회로 Half-adder, Full-adder, Ripple-carry Adder 및 Carry Look-ahead Adder로 진화했습니다.

이러한 Carry Look-ahead Adder 중에는 더 빠른 가산기 회로가 있습니다. 더 복잡한 하드웨어 회로를 사용하여 추가 중에 발생하는 전파 지연을 줄입니다. 가산기의 캐리 로직이 2 단계 로직으로 변경되도록 리플-캐리 가산기 회로를 변환하여 설계되었습니다.

4 비트 캐리 미리보기 가산기

병렬 가산기에서 각 완전 가산기의 캐리 출력은 다음 상위 상태에 대한 캐리 입력으로 제공됩니다. 따라서 이러한 가산기는 해당 상태에 대해 캐리 입력을 사용할 수없는 경우 모든 상태의 캐리 및 합계 출력을 생성 할 수 없습니다.

따라서 계산이 발생하려면 회로는 캐리 비트가 모든 상태로 전파 될 때까지 기다려야합니다. 이것은 회로에서 전달 전파 지연을 유도합니다.

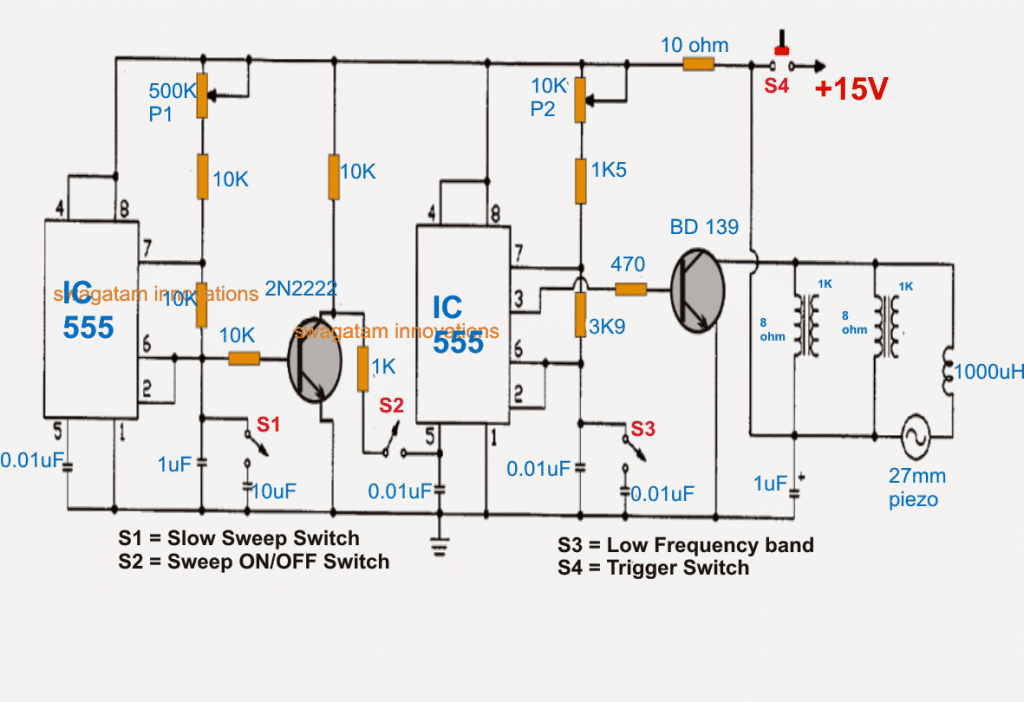

4 비트 리플 캐리 가산기

위의 4 비트 리플 캐리 가산기 회로를 고려하십시오. 여기서 S3의 합계는 입력 A3 및 B3이 제공되는 즉시 생성 될 수 있습니다. 그러나 캐리 C3는 캐리 비트 C2가 적용될 때까지 계산할 수 없지만 C2는 C1에 의존합니다. 따라서 최종 정상 상태 결과를 생성하려면 캐리가 모든 상태를 통해 전파되어야합니다. 이것은 회로의 캐리 전파 지연을 증가시킵니다.

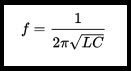

가산기의 전파 지연은 '각 게이트의 전파 지연에 회로의 단 수를 곱한 값'으로 계산됩니다. 많은 수의 비트를 계산하려면 더 많은 단계를 추가해야하므로 지연이 훨씬 더 심해집니다. 따라서 이러한 상황을 해결하기 위해 Carry Look-ahead Adder가 도입되었습니다.

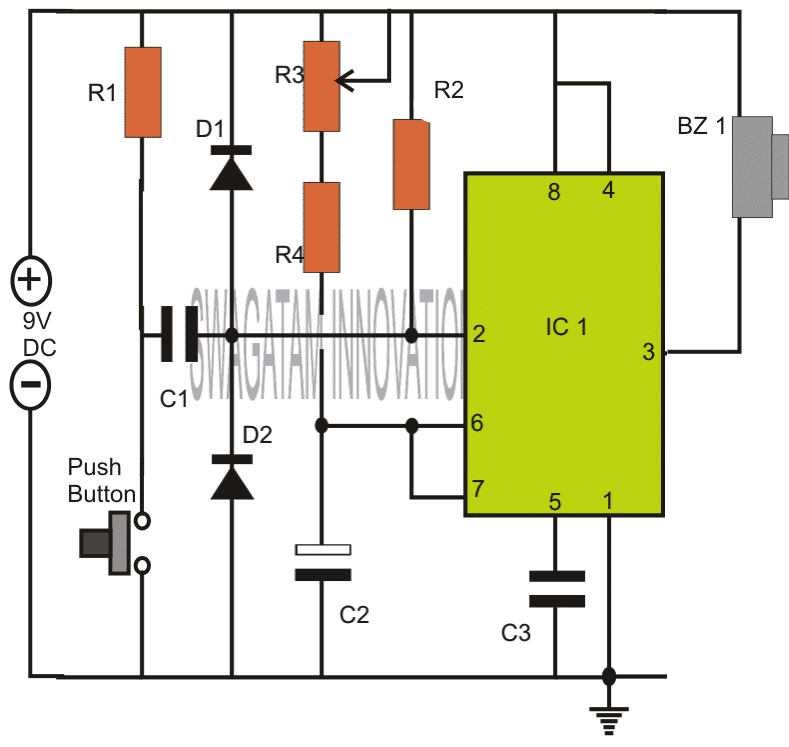

Carry Look-ahead Adder의 기능을 이해하기 위해 4 비트 Carry Look-ahead Adder가 아래에 설명되어 있습니다.

4 비트 캐리 미리보기 가산기 논리 다이어그램

이 가산기에서 가산기의 모든 단계에서 캐리 입력은 독립 단계에서 생성 된 캐리 비트와 독립적입니다. 여기서 모든 단계의 출력은 이전 단계에서 추가 된 비트와 시작 단계에서 제공된 캐리 입력에만 의존합니다. 따라서 어느 단계의 회로도 이전 단계에서 캐리 비트 생성을 기다릴 필요가 없으며 캐리 비트는 언제든지 평가할 수 있습니다.

캐리 미리보기 가산기의 진실 표

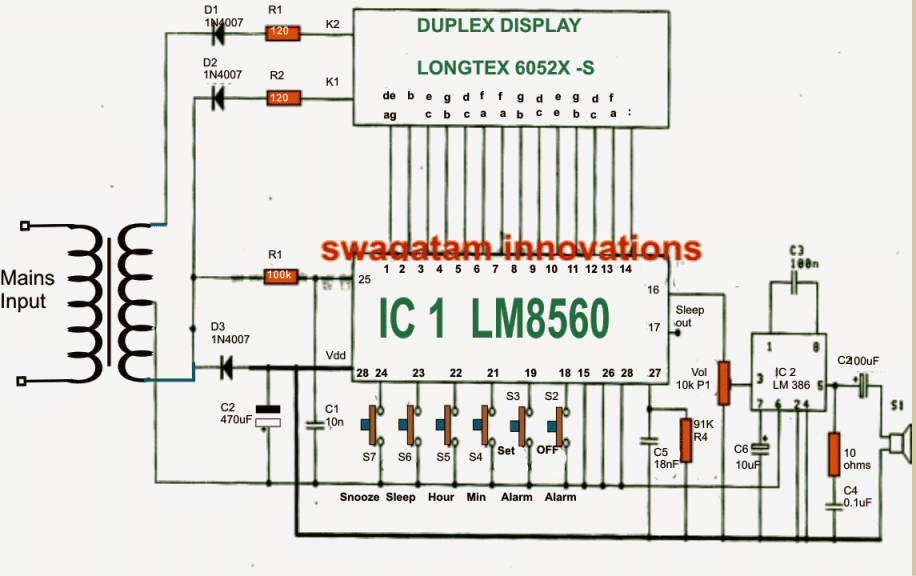

이 가산기의 진리표를 도출하기 위해 두 가지 새로운 용어 인 Carry 생성 및 전달 전파가 도입되었습니다. 캐리는 캐리 Ci + 1이 생성 될 때마다 Gi = 1을 생성합니다. Ai 및 Bi 입력에 따라 다릅니다. Ai와 Bi가 모두 1 일 때 Gi는 1입니다. 따라서 Gi는 Gi = Ai로 계산됩니다. Bi.

캐리 전파 된 Pi는 Ci에서 Ci + 1 로의 캐리 전파와 연관됩니다. Pi = Ai ⊕ Bi로 계산됩니다. 이 가산기의 진리표는 완전 가산기의 진리표를 수정하여 파생 될 수 있습니다.

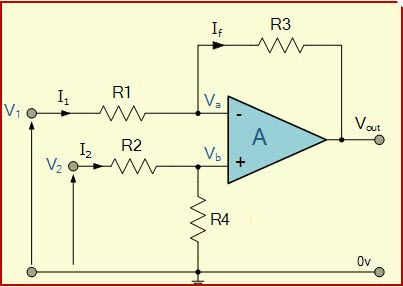

Gi 및 Pi 용어를 사용하여 Sum Si 및 Carry Ci + 1은 다음과 같습니다.

- Si = Pi ⊕ Gi.

- Ci + 1 = Ci.Pi + Gi.

따라서 캐리 비트 C1, C2, C3 및 C4는 다음과 같이 계산할 수 있습니다.

- C1 = C0.P0 + G0.

- C2 = C1.P1 + G1 = (C0.P0 + G0) .P1 + G1.

- C3 = C2.P2 + G2 = (C1.P1 + G1) .P2 + G2.

- C4 = C3.P3 + G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3.

Ci + 1을 전달하는 방정식은 중간 캐리 비트가 아니라 캐리 C0에만 의존하는 방정식에서 볼 수 있습니다.

캐리-조회-가산기-진실 표

회로도

위의 방정식은 AND, OR 게이트와 함께 2 단계 조합 회로를 사용하여 구현됩니다. 여기서 게이트는 여러 입력을 가지고 있다고 가정합니다.

Carry-Output-Generation-Circuit-of-Carry-Look-Ahead-Adder

4 비트에 대한 Carry Look-ahead Adder 회로는 다음과 같습니다.

4 비트 캐리-예측-가산기-회로 다이어그램

8 비트 및 16 비트 Carry Look-ahead Adder 회로는 4 비트 가산기 회로를 캐리 로직으로 계단식으로 연결하여 설계 할 수 있습니다.

캐리 미리보기 가산기의 장점

이 가산기에서는 전파 지연이 감소합니다. 모든 단계의 캐리 출력은 시작 단계의 초기 캐리 비트에만 의존합니다. 이 가산기를 사용하여 중간 결과를 계산할 수 있습니다. 이 가산기는 계산에 사용되는 가장 빠른 가산기입니다.

응용

고속 Carry Look-ahead Adder는 IC로 구현 된대로 사용됩니다. 따라서 회로에 가산기를 삽입하는 것은 쉽습니다. 두 개 이상의 가산기를 결합하여 더 높은 비트 부울 함수의 계산을 쉽게 수행 할 수 있습니다. 여기서 게이트 수의 증가는 더 높은 비트에 사용될 때도 적당합니다.

이 가산기의 경우 면적과 속도 사이에 상충 관계가 있습니다. 더 높은 비트 계산에 사용하면 고속을 제공하지만 회로의 복잡성도 증가하여 회로가 차지하는 영역이 증가합니다. 이 가산기는 일반적으로 더 높은 계산에 사용될 때 함께 계단식으로 연결된 4 비트 모듈로 구현됩니다. 이 가산기는 다른 가산기에 비해 비용이 많이 듭니다.

컴퓨터의 부울 계산을 위해 가산기가 정기적으로 사용됩니다. Charles Babbage는 컴퓨터의 캐리 비트를 예상하는 메커니즘을 구현하여 잔물결 캐리 가산기 . 시스템을 설계하는 동안 계산 속도는 설계자에게 가장 중요한 결정 요소입니다. 1957 년 Gerald B. Rosenberger는 현대적인 Binary Carry Look-ahead Adder의 특허를 받았습니다. 게이트 지연 및 시뮬레이션 분석을 기반으로이 가산기의 회로를 더 빠르게 수정하기위한 실험이 수행되고 있습니다. n 비트 캐리 룩 어 헤드 가산기의 경우 각 게이트의 지연이 20 일 때 전파 지연은 얼마입니까?

이미지 크레딧