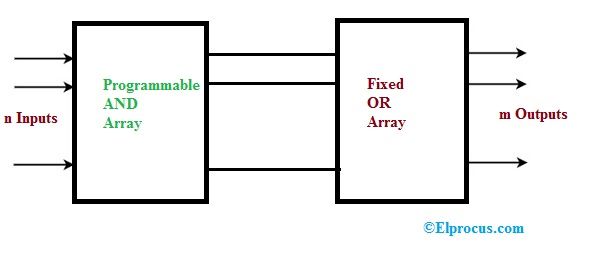

이진수를 십진수로 변환하는 것은 장치 즉 디코더를 사용하여 수행 할 수 있습니다. 이 장치는 n 입력 라인을 사용하여 2n 출력 라인을 생성하는 조합 논리 회로의 한 종류입니다. 여기에서이 장치의 출력은 2n 라인 미만일 수 있습니다. 여러 입력과 여러 출력을 포함하는 다양한 종류의 이진 디코더가 있습니다. 일부 종류의 디코더에는 데이터 입력과 함께 하나 이상의 인 에이블 입력이 포함됩니다. 활성화 입력이 비활성화 될 때마다 모든 출력이 비활성화됩니다. 그 기능에 따라 바이너리 디코더는 데이터를 n 입력 신호에서 2n 출력 신호로 변경합니다. 어떤 종류의 디코더에서는 2n 이하의 출력 라인을 가지고 있습니다. 따라서 이러한 상황에서 다양한 입력 값에 대해 최소 하나의 출력 프로토 타입이 반복 될 수 있습니다. 3 Line to 8 Line Decoder 및 4 Line to 16 Line Decoder와 같은 두 종류의 고차 디코더가 있습니다. 이 문서에서는 3 라인에서 8 라인 디코더에 대한 개요를 설명합니다.

디코더 란 무엇입니까?

디코더는 조합 논리 회로 코드를 신호 세트로 변경하는 데 사용됩니다. 인코더의 역 과정입니다. 디코더 회로는 여러 입력을 받아 여러 출력을 제공합니다. 디코더 회로는 'n'입력의 이진 데이터를 '2 ^ n'고유 출력으로 가져옵니다. 입력 핀 외에도 디코더에는 활성화 핀이 있습니다. 이렇게하면 핀이 무효화되어 회로를 비활성화 할 수 있습니다. 이 기사에서는 3 ~ 8 라인 디코더 및 디멀티플렉서에 대해 설명합니다.

아래는 A가 입력이고 D0과 D1이 출력 인 간단한 1 ~ 2 라인 디코더의 진리표입니다.

1 ~ 2 디코더

회로는 1-2 디코더 로직을 보여줍니다.

1 ~ 2 디코더 회로

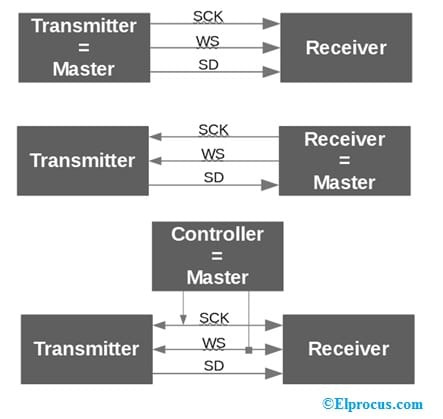

디멀티플렉서는 단일 입력을 받아 여러 출력 라인 중 하나를 제공하는 장치입니다. 디멀티플렉서는 하나의 단일 입력 데이터를 가져온 다음 한 번에 하나씩 단일 출력 라인 중 하나를 선택합니다. 그것은 멀티플렉서의 역 과정 . DEMUX 또는 데이터 배포 자라고도합니다. DEMUX는 입력 직렬 데이터 라인을 출력 병렬 데이터로 변환합니다. DEMUX는 단일 입력으로 'n'선택 라인에 대해 '2n'출력을 제공합니다.

Demux

DEMUX는 회로가 데이터 신호를 여러 장치 중 하나로 보내려고 할 때 사용됩니다. 디코더는 여러 장치 중에서 선택하는 데 사용되는 반면 디멀티플렉서는 신호를 여러 장치로 보내는 데 사용됩니다.

아래는 입력 데이터가“I”인 1 ~ 2 디멀티플렉서의 진리표입니다. D0과 D1은 출력 데이터 라인, A는 선택 라인입니다.

1 ~ 2 Demux 진실 표

회로는 1 대 2 디멀티플렉서 회로도를 보여줍니다.

1 ~ 2 Demux

디코더가 필요한 이유는 무엇입니까?

디코더의 주요 기능은 인코더와 반대이기 때문에 코드를 신호 세트로 변경하는 것이지만 디코더 설계는 간단합니다. 디코더와 디멀티플렉서의 주요 차이점은 하나의 입력 만 허용하고이를 출력 중 하나로 전달하는 데 사용되는 조합 회로입니다. 반면 디코더는 여러 입력을 허용하고 디코딩 된 출력을 생성합니다.

3 라인에서 8 라인 디코더 설계 단계

여기에서 3 라인 대 8 라인 디코더는 2 라인 대 4 라인 디코더와 같은 2 개의 하위 디코더로 설계된 고차 디코더입니다. 이 디코더를 구현하기 전에 2 라인 대 4 라인 디코더를 설계했습니다.

2 라인-4 라인 디코더

이 2 라인 대 4 라인 디코더에는 A0 및 A1과 같은 2 개의 입력과 Y0에서 Y4와 같은 4 개의 출력이 포함됩니다. 이 디코더의 블록 다이어그램은 다음과 같습니다.

2 라인-4 라인 디코더

입력과 활성화가 1이면 출력은 1이됩니다. 여기에 2-4 디코더의 진리표가 있습니다.

IS | A1 | A0 | Y3 | Y2 | Y1 | Y0 |

0 | 엑스 | 엑스 | 0 | 0 | 0 | 0 |

1 | 0 | 0 | 0 | 0 | 0 | 1 |

1 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 |

모든 출력에 대한 부울 표현식은 다음과 같습니다.

Y3 = E. A1. A0

Y2 = E. A1. A0 '

Y1 = E. A1 '. A0

Y0 = E. A1 '. A0 '

이 디코더의 모든 출력에는 하나의 제품 용어가 포함됩니다. 따라서 4 개의 제품 용어는 각 게이트에 3 개의 입력과 2 개의 인버터가 포함 된 4 개의 AND 게이트를 통해 구현 될 수 있습니다. 2-4 디코더 로직 다이어그램은 아래와 같습니다. 따라서이 디코더의 출력은 입력 및 활성화의 최소값 일뿐입니다. 활성화가 0이면 나중에 모든 디코더의 출력은 0과 같습니다. 마찬가지로, 3 라인 대 8 라인 디코더는 A0, A1 및 A2의 3 개 입력 변수에 대해 8 개의 minterm을 생성합니다.

2 ~ 4 디코더의 논리 다이어그램

3 라인에서 8 라인 디코더 구현

이 3 라인 대 8 라인 디코더의 구현은 2 개의 2 라인 대 4 라인 디코더를 사용하여 수행 할 수 있습니다. 위에서 2-4 라인 디코더에는 2 개의 입력과 4 개의 출력이 포함되어 있다고 설명했습니다. 따라서 3 라인에서 8 라인 디코더에는 A2, A1 및 A0과 같은 3 개의 입력과 Y7 – Y0의 8 개의 출력이 포함됩니다.

다음 공식은 고차 디코더 구현 하위 디코더의 도움으로

필요한 하위 디코더의 수는 다음과 같습니다. m2 / m1

어디,

하위 디코더의 o / ps 수는‘m1’입니다.

상위 디코더의 o / ps 수는‘m2’입니다.

예를 들어, m1 = 4 & m2 = 8이면 위의 방정식에서이 값을 대체하십시오. 우리는 필요한 아니오를 얻을 수 있습니다. 디코더의 수는 2 개입니다. 따라서 단일 3 ~ 8 디코더를 구현하려면 2 개의 2 라인에서 4 라인 디코더가 필요합니다. 여기서 블록 다이어그램은 2 ~ 4 개의 디코더를 사용하여 아래에 표시됩니다.

2-4 라인을 사용하는 3-8 디코더

A2, A1 및 A0과 같은 병렬 입력은 3 라인에서 8 라인 디코더에 제공됩니다. 여기서 A3의 칭찬은 디코더의 핀이 Y7 ~ Y0과 같은 출력을 얻을 수 있도록 제공됩니다. 이 출력은 더 낮은 8 분입니다. 위의 디코더에서 A3 입력은 핀이 Y15 – Y8에서 출력을 얻을 수 있도록 연결됩니다. 따라서 이러한 출력은 더 높은 8 분 용어입니다.

로직 게이트를 사용하는 3 라인 ~ 8 라인 디코더

3 ~ 8 라인 디코더에는 3 개의 입력과 8 개의 출력이 포함됩니다. 여기서 입력은 A, B & C를 통해 표현되는 반면 출력은 D0, D1, D2… D7을 통해 표현됩니다.

3 개의 입력을 기준으로 8 개의 출력을 선택할 수 있습니다. 따라서이 3 라인 대 8 라인 디코더의 진리표가 아래에 나와 있습니다. 다음 진리표에서 DO – D7의 8 개 출력 중 하나가 3 개의 선택 입력에 따라 선택 될 수 있음을 알 수 있습니다.

| 에 | 비 | 씨 | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

위의 3 줄 진리표에서 8 줄 디코더까지 논리식은 다음과 같이 정의 할 수 있습니다.

D0 = A’B’C’

D1 = A’B’C

D2 = A’BC’

D3 = A’BC

D4 = AB’C’

D5 = AB’C

D6 = ABC’

D7 = ABC

위의 부울 표현식에서 3 ~ 8 디코더 회로의 구현은 3 개의 NOT 게이트와 8 ~ 3 개의 입력 AND 게이트의 도움으로 수행 될 수 있습니다.

위의 회로에서 3 개의 입력은 8 개의 출력으로 디코딩 될 수 있으며, 여기서 모든 출력은 3 개의 입력 변수 중 중간 항 중 하나를 나타냅니다.

위의 논리 회로에있는 3 개의 인버터는 입력의 보완을 제공하고 각각의 AND 게이트는 중간 단자 중 하나를 생성합니다.

이러한 종류의 디코더는 주로 모든 3 비트 코드를 디코딩하는 데 사용되며 입력 코드에 대해 8 개의 다른 조합에 해당하는 8 개의 출력을 생성합니다.

이 디코더는이 디코더의 입력이 3 비트 이진수를 나타내는 반면 출력은 8 진수 시스템 내에서 8 자리를 나타 내기 때문에 이진수에서 8 진수 디코더로도 알려져 있습니다.

3 라인 ~ 8 라인 디코더 블록 다이어그램

이 디코더 회로는 3 개의 입력에 대해 8 개의 로직 출력을 제공하고 활성화 핀을 가지고 있습니다. 회로는 AND 및 NAND 논리 게이트로 설계되었습니다. 3 개의 바이너리 입력을 받아 8 개의 출력 중 하나를 활성화합니다. 3 ~ 8 라인 디코더 회로 8 진 디코더에 대한 바이너리라고도합니다.

3 ~ 8 라인 디코더 블록 다이어그램

디코더 회로는 활성화 핀 (E)이 높을 때만 작동합니다. S0, S1 및 S2는 D0, D1, D2, D3의 세 가지 다른 입력입니다. D4. D5. D6. D7은 8 개의 출력입니다. 그만큼 3 ~ 8 라인 디코더의 로직 다이어그램 아래에 나와 있습니다.

3 ~ 8 디코더 회로

3 ~ 8 라인 디코더 및 진실 표

아래 표는 3 ~ 8 라인 디코더의 진리표입니다.

| S0 | S1 | S2 | IS | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

| 엑스 | 엑스 | 엑스 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

활성화 핀 (E)이 로우이면 모든 출력 핀이 로우입니다.

1 ~ 8 디멀티플렉서

에 1 라인 ~ 8 라인 디멀티플렉서 1 개의 입력, 3 개의 선택 입력 라인 및 8 개의 출력 라인이 있습니다. 선택한 입력에 따라 하나의 입력 데이터를 8 개의 출력 라인으로 분배합니다. Din은 입력 데이터이고 S0, S1 및 S2는 선택 입력이며 Y0, Y1, Y2, Y3, Y4, Y5, Y6, Y7은 출력입니다.

1 ~ 8 DEMUX

1-8 demux 회로의 회로도는 아래와 같습니다.

1 ~ 8 Demux 회로

3 ~ 8 디코더 / 디멀티플렉서

3 ~ 8 라인 디코더 IC 74HC238은 디코더 / 디멀티플렉서로 사용됩니다. 3 ~ 8 라인 디코더 디멀티플렉서는 디코더와 디멀티플렉서로 모두 사용할 수있는 조합 회로입니다. IC 74HC238은 3 개의 이진 주소 입력 (A0, A1, A2)을 8 개의 출력 (Y0 ~ Y7)으로 디코딩합니다. 이 장치에는 세 개의 활성화 핀도 있습니다. 디멀티플렉서로 동일한 조합이 사용됩니다.

핀 구성

아래는 IC74HC238 3 ~ 8 라인 디코더 또는 디멀티플렉서의 핀 구성입니다. 16 핀 DIP입니다.

회로

논리 회로는 IC 74HC238의 작동을 설명합니다.

74HC238 IC의 특징

- 역 다중화 기능

- 다중 입력으로 손쉬운 확장 가능

- 메모리 칩 선택 디코딩에 이상적

- 활성 HIGH 상호 배타적 인 출력

- 여러 패키지 옵션

디코더 적용

- 그만큼 디코더 아날로그 디코더에서 아날로그에서 디지털로의 변환에 사용되었습니다.

- 명령을 CPU 제어 신호로 변환하기 위해 전자 회로에서 사용됩니다.

- 그들은 주로 사용 논리 회로 , 데이터 전송.

디멀티플렉서의 응용

- 단일 소스를 여러 대상에 연결하는 데 사용됩니다.

- Demux는 통신 시스템에서 여러 데이터 신호를 단일 전송 라인으로 전달하는 데 사용됩니다.

- 산술 논리 장치에 사용

- 데이터 통신에서 직렬-병렬 변환기에 사용됩니다.

따라서 이것이 3 ~ 8 라인 디코더와 디멀티플렉서에 대한 기본 정보입니다. 디지털 논리 회로와 진리표 및 그 응용 프로그램을 관찰하여이 주제에 대한 몇 가지 기본 개념을 얻었기를 바랍니다. 또한,이 기사 또는 최신 전자 프로젝트 , 아래 댓글 섹션에서이 주제에 대한 의견을 작성할 수 있습니다.