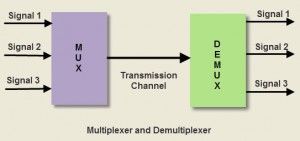

컴퓨터 프로그램을 실행하려면 컴퓨터의 두 개 이상의 구성 요소가 동시에 작동해야합니다. 예를 들면 프로세서 – 필요한 제어 정보, 주소… 등, 버스 제공 – 정보와 데이터를 메모리에서 I / O 장치로 전송하기 위해… 시스템의 흥미로운 요소는 프로세서, 메모리 및 I / O 장치 간의 정보 전송을 처리하는 방식입니다. 일반적으로 프로세서는 전송 시작부터 대상의 데이터 저장소까지 데이터 전송의 모든 프로세스를 제어합니다. 이는 프로세서에 부하를 추가하고 대부분의 경우 이상적인 상태를 유지하므로 시스템의 효율성이 저하됩니다. I / O 장치와 메모리 간의 데이터 전송 속도를 높이기 위해 DMA 컨트롤러는 스테이션 마스터 역할을합니다. DMA 컨트롤러는 프로세서의 개입을 최소화하면서 데이터를 전송합니다.

DMA 컨트롤러 란?

DMA라는 용어는 직접 메모리 액세스를 나타냅니다. 직접 메모리 액세스에 사용되는 하드웨어 장치를 DMA 컨트롤러라고합니다. DMA 컨트롤러는 제어 장치입니다. , I / O 장치의 일부 인터페이스 회로 , 프로세서의 개입을 최소화하면서 I / O 장치와 주 메모리간에 데이터 블록을 전송할 수 있습니다.

컴퓨터 아키텍처의 DMA 컨트롤러 다이어그램

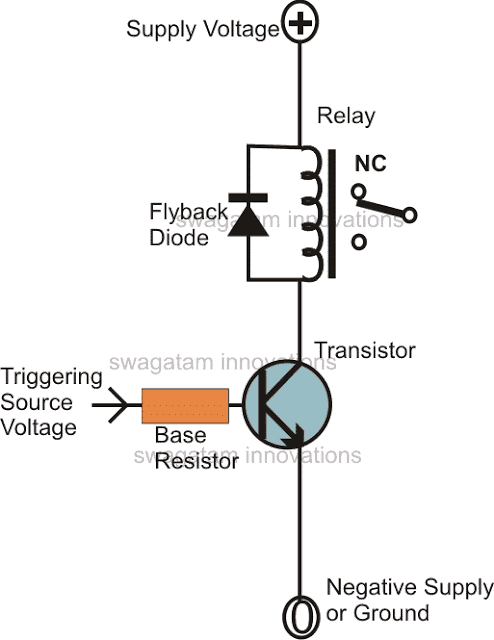

DMA 컨트롤러는 버스와 입출력 장치 간의 인터페이스를 제공합니다. 프로세서의 개입없이 데이터를 전송하지만 프로세서에 의해 제어됩니다. 프로세서는 시작 주소, 데이터 블록의 단어 수 및 데이터 전송 방향을 전송하여 DMA 컨트롤러를 시작합니다. I / O 장치에서 메모리로 또는 주 메모리에서 I / O 장치로. 하나 이상의 외부 장치를 DMA 컨트롤러에 연결할 수 있습니다.

컴퓨터 아키텍처의 DMA

DMA 컨트롤러에는 주소를 생성하고 전송할 I / O 장치를 선택하기위한 주소 단위가 포함되어 있습니다. 또한 전송 된 블록 수를 유지하고 데이터 전송 방향을 표시하기위한 제어 장치 및 데이터 수를 포함합니다. 전송이 완료되면 DMA는 인터럽트를 발생시켜 프로세서에 알립니다. DMA 컨트롤러의 일반적인 블록 다이어그램은 아래 그림에 나와 있습니다.

DMA 컨트롤러의 일반적인 블록 다이어그램

DMA 컨트롤러 작동

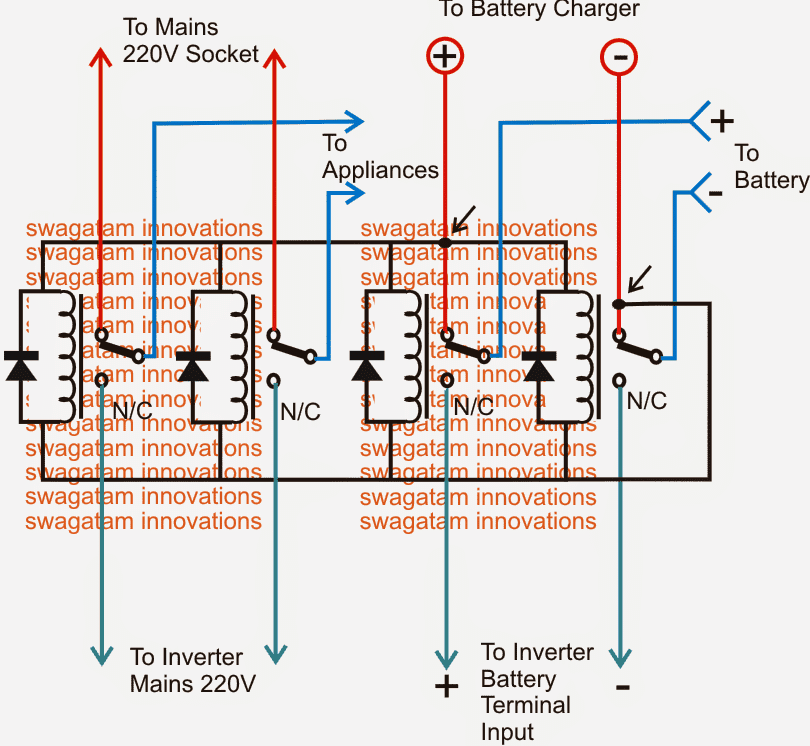

DMA 컨트롤러는 데이터 전송을 위해 프로세서와 버스를 공유해야합니다. 주어진 시간에 버스를 보유하는 장치를 버스 마스터라고합니다. I / O 장치에서 메모리로 또는 그 반대로 전송해야하는 경우 프로세서는 현재 프로그램의 실행을 중지하고 증분합니다. 프로그램 카운터는 스택을 통해 데이터를 이동 한 다음 주소 버스를 통해 DMA 컨트롤러에 DMA 선택 신호를 보냅니다.

DMA 컨트롤러가 비어 있으면 버스 요청 신호를 발생시켜 프로세서에 버스 제어를 요청합니다. 프로세서는 버스 승인 신호를 발생시켜 컨트롤러에 버스를 승인합니다. 이제 DMA 컨트롤러가 버스 마스터입니다. 프로세서는 메모리 주소, 전송할 데이터 블록 수 및 데이터 전송 방향을 전송하여 DMA 컨트롤러를 시작합니다. 데이터 전송 작업을 DMA 컨트롤러에 할당 한 후 이상적으로 데이터 전송이 완료 될 때까지 기다리는 대신 프로세서는 스택에서 명령을 검색 한 후 프로그램 실행을 다시 시작합니다.

DMA 컨트롤러에 의한 컴퓨터의 데이터 전송

“n형 반도체 대 p형 ”

DMA 컨트롤러는 이제 버스를 완벽하게 제어하고 CPU와 관계없이 메모리 및 I / O 장치와 직접 상호 작용할 수 있습니다. 프로세서가 수신 한 제어 명령에 따라 데이터를 전송합니다. 데이터 전송이 완료되면 버스 요청 신호를 비활성화하고 CPU는 버스 승인 신호를 비활성화하여 버스 제어를 CPU로 이동합니다.

I / O 장치가 전송을 시작하려고 할 때 DMA 컨트롤러에 DMA 요청 신호를 전송하고 컨트롤러가 비어 있는지 확인합니다. 그런 다음 컨트롤러는 버스에 대한 프로세서를 요청하여 버스 요청 신호를 발생시킵니다. 버스 승인 신호를받은 후 장치에서 데이터를 전송합니다. n 채널 DMA 컨트롤러의 경우 n 개의 외부 장치를 연결할 수 있습니다.

DMA는 다음을 포함하는 세 가지 모드로 데이터를 전송합니다.

에) 버스트 모드 :이 모드에서 DMA는 전체 데이터 전송이 완료된 후에 만 버스를 CPU로 핸드 오버합니다. 한편, CPU가 버스를 필요로한다면 이상적인 상태를 유지하고 데이터 전송을 기다려야합니다.

비) 사이클 스틸 링 모드 :이 모드에서 DMA는 모든 바이트를 전송 한 후 CPU로 버스를 제어합니다. 지속적으로 버스 제어 요청을 발행하고 1 바이트를 전송하고 버스를 반환합니다. 이 CPU는 더 높은 우선 순위 작업을위한 버스가 필요한 경우 오랫동안 기다릴 필요가 없습니다.

씨) 투명 모드 : 여기서 DMA는 CPU가 버스를 사용할 필요가없는 명령을 실행할 때만 데이터를 전송합니다.

8237 DMA 컨트롤러

- 8237에는 채널 수를 늘리는 유연성과 함께 4 개의 I / O 채널이 있습니다.

- 각 채널은 개별적으로 프로그래밍 할 수 있으며 64k 주소 및 데이터 기능이 있습니다.

- 타이밍 제어 블록, 프로그램 명령 제어 블록, Priority Encoder Block은 8237A의 세 가지 주요 블록입니다.

- 내부 타이밍 및 외부 제어 신호는 타이밍 제어 블록에 의해 구동됩니다.

- 마이크로 프로세서가 DMA에 제공하는 다양한 명령은 프로그램 명령 제어 블록에 의해 디코딩됩니다.

- 가장 높은 우선 순위를 부여해야하는 채널은 우선 순위에 따라 결정됩니다. 인코더 블록 .

8237A에는 27 개의 내부 레지스터가 있습니다.

8237A는 이상적인 사이클과 활성 사이클의 두 사이클로 작동하며, 각 사이클은 각각 하나의 클록 주기로 구성된 7 개의 개별 상태를 포함합니다.

S0- 컨트롤러가 버스를 요청하고 프로세서의 승인을 기다리는 첫 번째 상태입니다.

S1, S2, S3, S4는 실제 데이터 전송이 이루어지는 8237A의 작동 상태라고합니다. 전송 대기 상태에 더 많은 시간이 필요한 경우 이러한 상태 사이에 SW가 추가됩니다.

메모리-메모리 전송의 경우 메모리에서 읽기 및 메모리에 쓰기 전송이 이루어져야합니다. 단일 전송에는 8 개 상태가 필요합니다. 아래 첨자 S11, S12, S13, S14가있는 처음 4 개 상태는 메모리에서 읽기 전송을 수행하고 다음 4 개 S21, S22, S23, S24는 메모리에 쓰기 전송을위한 것입니다.

DMA는 서비스를 요청하는 채널이 없을 때 이상적인 상태가되어 SI 상태를 수행합니다. SI는 요청을받을 때까지 DMA가 비활성 상태 인 비활성 상태입니다. 이 상태에서 DMA는 프로세서가 DMA를 프로그래밍 할 수있는 프로그램 상태입니다.

DMA가 이상적인 상태에 있고 더 이상 채널 요청을받지 못하면 HRQ 신호를 프로세서에 출력하고 버스트 모드, 사이클 도용 모드 또는 투명 모드로 데이터 전송을 시작할 수있는 활성 상태로 들어갑니다.

8237 핀 다이어그램

8257 DMA 컨트롤러

단일 Intel 8212 I / O 포트 장치와 함께 사용하면 8257 DMA 컨트롤러가 완전한 4 채널을 형성합니다. DMA 컨트롤러 . 전송 요청을 받으면 8257 컨트롤러-

- 프로세서에서 시스템 버스에 대한 제어권을 얻습니다.

- 우선 순위가 가장 높은 채널에 연결된 주변 장치가 인식됩니다.

- 메모리 주소의 최하위 비트는 시스템 버스의 주소 라인 A0-A7 위로 이동됩니다.

- 가장 중요한 8 비트 메모리 주소의 데이터 라인을 통해 8212 I / O 포트로 구동됩니다.

- 주변 장치와 주소 지정된 메모리 위치 간의 데이터 전송을위한 적절한 제어 신호를 생성합니다.

- 지정된 수의 바이트가 전송되면 컨트롤러는 터미널 카운트 (TC) 출력을 활성화하여 CPU 전송 종료를 알립니다.

각 채널 8257에는 두 개의 16 비트 레지스터 – 1) DMA 주소 레지스터 및 2) 터미널 카운트 레지스터. 채널이 활성화되기 전에 초기화되어야합니다. 액세스 할 첫 번째 메모리 위치의 주소는 DMA 주소 레지스터에로드됩니다. 터미널 카운트 레지스터에로드 된 값의 하위 14 비트는 터미널 카운트 출력이 활성화되기 전의 DMA 사이클 수에서 1을 뺀 값을 나타냅니다. 채널에 대한 작업 유형은 터미널 카운트 레지스터의 최상위 2 비트로 표시됩니다.

8257 핀 다이어그램

DMA 컨트롤러의 장단점

DMA 컨트롤러의 장단점은 다음과 같습니다.

장점

- DMA는 CPU의 개입을 우회하여 메모리 작업 속도를 높입니다.

- CPU의 작업 과부하가 감소합니다.

- 각 전송에 대해 몇 개의 클록 사이클 만 필요합니다.

단점

- 캐시 일관성 문제는 DMA가 데이터 전송에 사용될 때 볼 수 있습니다.

- 시스템 가격을 올립니다.

DMA ( 직접 메모리 액세스 ) 컨트롤러는 그래픽 카드, 네트워크 카드, 사운드 카드 등에 사용되고 있습니다. DMA는 멀티 코어 프로세서의 칩 내 전송에도 사용됩니다. 세 가지 모드 중 하나로 작동하는 DMA는 프로세서의 부하를 상당히 줄일 수 있습니다. 어떤 DMA 모드에서 작업 했습니까? 어떤 모드가 더 효과적이라고 생각하십니까?