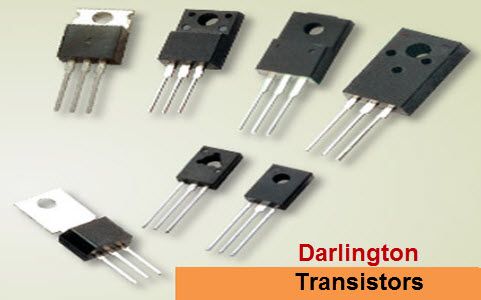

현재 존재하는 두 가지 주요 유형의 FET는 다음과 같습니다. JFET 및 MOSFET.

MOSFET은 공핍 유형과 향상 유형. 이 두 유형 모두 MOSFET의 기본 작동 모드를 정의하는 반면, MOSFET이라는 용어는 금속 산화물 반도체 전계 효과 트랜지스터의 약어입니다.

두 가지 유형이 서로 다른 작업 특성을 가지고 있기 때문에 우리는 서로 다른 기사에서 각각을 개별적으로 평가할 것입니다.

향상 및 공핍 MOSFET의 차이점

기본적으로 향상 MOSFET과 달리 공핍 MOSFET은 게이트-소스 단자 (VGS)에 0V가있는 경우에도 온 상태입니다.

강화 MOSFET의 경우 게이트-소스 전압 (VGS)이 게이트-소스 임계 전압 (VGS (th))보다 높아야합니다. 그것을 수행하기 위해 .

그러나 N 채널 공핍 MOSFET의 경우 VGS (th) 값이 0V 이상입니다. 이는 VGS = 0V 인 경우에도 공핍 MOSFET이 전류를 전도 할 수 있음을 의미합니다. 이를 끄려면 공핍 MOSFET의 VGS를 VGS (th) (음수) 아래로 줄여야합니다.

이 기사에서는 JFET와 일치하는 특성을 갖는 공 핍형 MOSFET에 대해 설명합니다. 유사성은 I 근처의 컷오프와 채도 사이입니다.DSS.

기본 구조

그림 5.23은 n 채널 공 핍형 MOSFET의 기본 내부 구조를 보여줍니다.

실리콘베이스를 사용하여 생성 된 p 형 재료 블록을 찾을 수 있습니다. 이 블록을 기판이라고합니다.

기판은 MOSFET이 구성되는 기초 또는 기초입니다. 일부 MOSFET의 경우 내부적으로 '소스'단자와 연결되어 있습니다. 또한 많은 장치가 그림 5.23에 나와있는 것처럼 4 단자 MOSFET을 특징으로하는 SS 형태의 추가 출력을 제공합니다.

드레인 및 소스 단자는 동일한 그림에 표시된 것처럼 전도성 접점을 통해 n- 도핑 된 위치에 연결되고 n- 채널을 통해 연결됩니다.

게이트는 미세한 이산화 규소 (SiO) 층을 통해 n- 채널과 절연되어 있지만 금속 층에도 연결되어 있습니다.두).

SiO두유전체라는 고유 한 형태의 절연 특성을 가지고있어 외부에서인가 된 전기장에 반응하여 자체적으로 반대 전기장을 생성합니다.

절연 층이기 때문에 재료 SiO두다음과 같은 중요한 정보를 제공합니다.

이 재료로 게이트 터미널과 MOSFET 채널 사이에 완전한 절연이 개발됩니다.

또한 SiO 때문입니다.두, MOSFET의 게이트는 매우 높은 수준의 입력 임피던스를 제공 할 수 있습니다.

이 중요한 높은 입력 임피던스 특성으로 인해 게이트 전류 I지모든 dc 바이어스 MOSFET 구성에 대해 사실상 제로 암페어입니다.

기본 작동 및 특성

그림 5.24에서 볼 수 있듯이 게이트 대 소스 전압은 두 단자를 함께 연결하여 0V로 구성되었으며 전압 VDS드레인 및 소스 단자에 적용됩니다.

위의 설정으로 드레인 측은 JFET 채널을 통한 등가 전류와 함께 n 채널 자유 전자에 의해 양의 전위를 설정합니다. 또한 결과 전류 VGS= 0V는 여전히 I로 식별됩니다.DSS, 그림 5.25와 같이

그림 5.26에서 게이트 소스 전압 VGS-1V의 형태로 음의 전위가 주어집니다.

이 음전위는 전자를 p- 채널 기판쪽으로 강제하고 (전하가 반발하기 때문에) p- 채널 기판에서 정공을 끌어 당깁니다 (반대 전하가 끌어 당기기 때문에).

이 네거티브 바이어스 V의 크기에 따라GS즉, 정공과 전자의 재결합이 발생하여 전도에 사용할 수있는 n- 채널에서 자유 전자가 감소합니다. 더 높은 수준의 부정적인 편향은 더 높은 재결합 비율을 초래합니다.

결과적으로 드레인 전류는 위의 네거티브 바이어스 조건이 증가함에 따라 감소하며 이는 V에 대해 그림 5.25에서 입증되었습니다.GSV 수준GS= -1, -2 등, -6V의 핀치 오프 표시까지.

결과적으로 전송 곡선 플롯과 함께 드레인 전류는 다음과 같이 진행됩니다. JFET.

자, 양의 VGS값에서 게이트 포지티브는 역 누설 전류로 인해 p 형 기판에서 과잉 전자 (자유 캐리어)를 끌어들입니다. 이것은 가속하는 입자들에 걸쳐 발생하는 충돌을 통해 새로운 캐리어를 만들 것입니다.

게이트-소스 전압이 양의 속도로 상승하는 경향이 있기 때문에 드레인 전류는 위에서 설명한 것과 동일한 이유로 그림 5.25에서 입증 된 것처럼 급격한 증가를 보입니다.

V의 곡선 사이에 생긴 간격GS= 0V 및 VGS= +1은 V의 1-V 변동으로 인해 전류가 증가한 양을 명확하게 보여줍니다.GS

드레인 전류의 빠른 상승으로 인해 최대 전류 정격에주의해야합니다. 그렇지 않으면 양의 게이트 전압 제한을 넘어갈 수 있습니다.

예를 들어 그림 5.25에 표시된 장치 유형의 경우 V를 적용합니다.GS= + 4V로 인해 드레인 전류가 22.2mA에서 상승하여 장치의 최대 항복 한계 (전류)를 초과 할 수 있습니다.

위의 조건은 양의 게이트-소스 전압을 사용하면 V가 아닌 경우 채널의 자유 캐리어 양에 향상된 효과를 생성한다는 것을 보여줍니다.GS= 0V.

이것이 드레인 또는 전송 특성의 양의 게이트 전압 영역이 일반적으로 향상 영역 . 이 영역은 I의 컷오프와 채도 수준 사이에 있습니다.DSS또는 고갈 지역.

예제 문제 해결

장점 및 응용

게이트-소스 전압이 0 일 때 드레인 전류가 0으로 떨어지는 향상 모드 MOSFET과 달리 최신 공핍 모드 FET는 게이트 전압이 0 인 눈에 띄는 전류를 제공합니다. 정확히 말하면, 드레인-소스 저항은 일반적으로 제로 전압에서 100 Ohms입니다.

위의 그래프에서 알 수 있듯이 ON 저항 rds(의 위에)대 아날로그 신호 범위는 거의 평탄한 응답처럼 보입니다. 이러한 고급 공 핍형 장치의 낮은 커패시턴스 수준과 함께 이러한 특성은 오디오 및 비디오 스위칭 애플리케이션을위한 아날로그 스위치로 특히 이상적입니다.

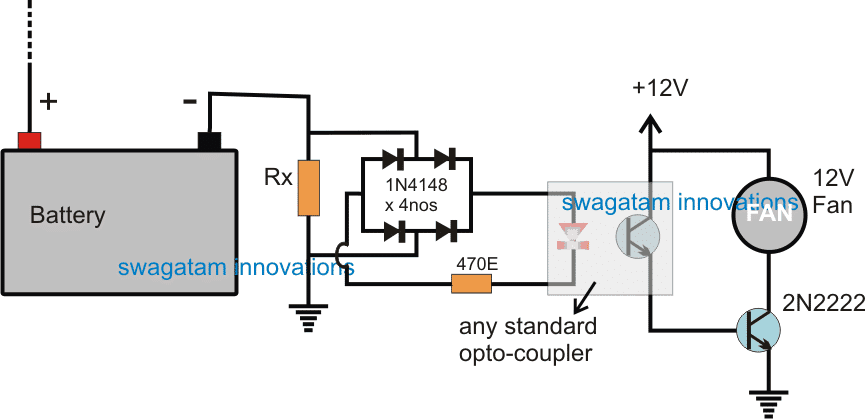

공핍 모드 MOSFET의 'normally-on'속성을 통해이 소자는 단일 FET 전류 조정기에 완벽하게 적합합니다.

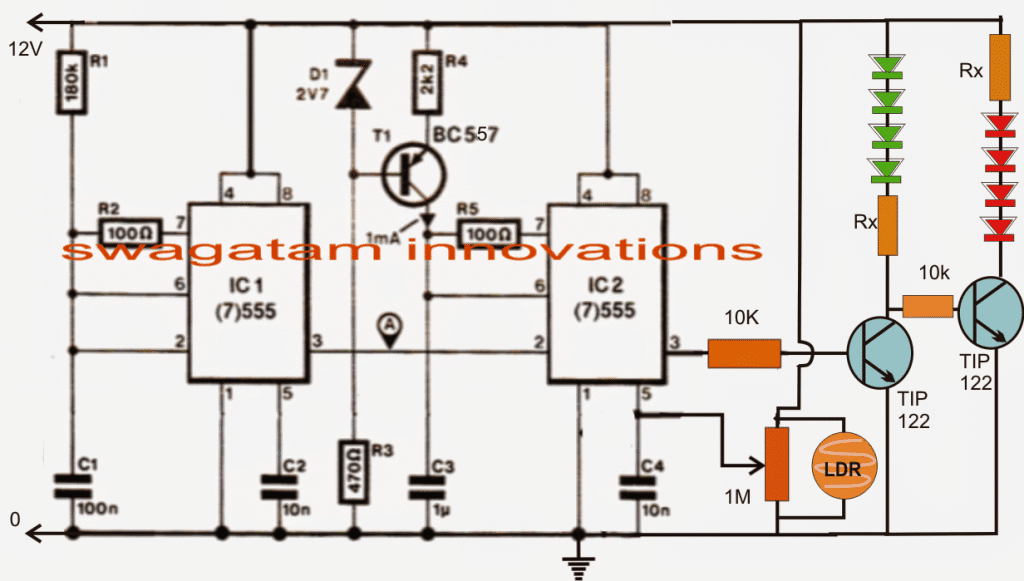

이러한 예제 회로 중 하나는 다음 그림에서 볼 수 있습니다.

Rs 값은 다음 공식을 사용하여 결정할 수 있습니다.

아르 자형에스= VGS떨어져서[1-(I디/나는DSS)1/2] / 나디

어디 나는디 출력에 필요한 조정 된 전류의 양입니다.

전류 소스 애플리케이션에서 공핍 모드 MOSFET의 주요 이점은 최소 드레인 커패시턴스로, 낮은 입력 누설, 중간 속도 (> 50V / us) 회로의 바이어스 애플리케이션에 적합합니다.

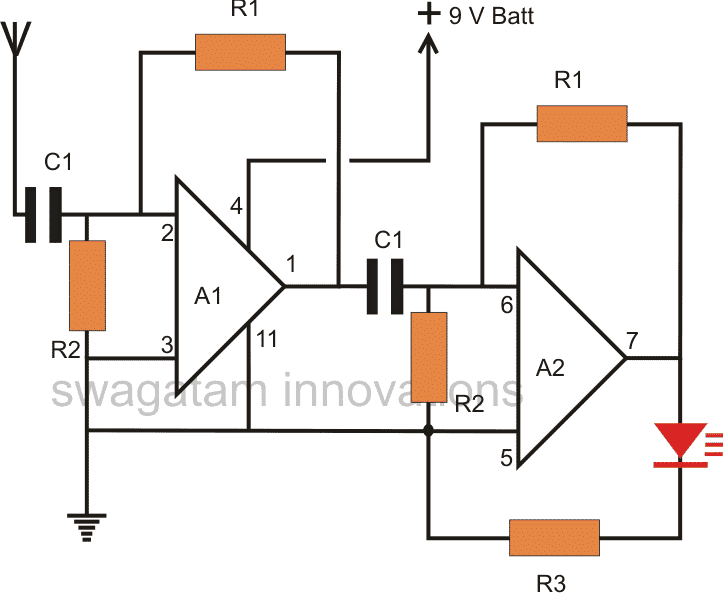

아래 그림은 이중 저 누설 기능 FET를 사용하는 저 입력 누설 전류 차동 프런트 엔드를 보여줍니다.

일반적으로 JFET의 양쪽은 ID = 500uA로 바이어스됩니다. 따라서 충전 보상 및 표유 커패시턴스를 위해 얻을 수있는 전류는 2ID 또는 이와 같은 경우 1.0mA로 제한됩니다. JFET의 해당 기능은 생산이 입증되었으며 데이터 시트에서 보장됩니다.

Cs는 입력단 '꼬리'전류 소스의 출력 커패시턴스를 상징합니다. 이 커패시턴스는 비 반전 증폭기에서 중요합니다. 입력단이이 네트워크 전체에서 상당한 신호 교환을 경험하고 Cs의 충전 전류가 클 수 있기 때문입니다. 정상적인 전류 소스를 사용하는 경우이 테일 커패시턴스는 비 반전 회로에서 눈에 띄는 슬 루율 저하를 초래할 수 있습니다 (Cs의 충전 전류가 최소 인 경향이있는 반전 애플리케이션과 비교).

슬 루율의 하락은 다음과 같이 표현할 수 있습니다.

1 / 1 + (Cs / Sc)

Cs가 Cc (보상 커패시터)보다 낮은 한 슬 루율에 거의 변동이 없을 수 있습니다. DMOS FET를 사용하면 Cs는 약 2pF가 될 수 있습니다. 이 전략은 슬 루율을 크게 향상시킵니다. 1 ~ 5mA보다 높은 전류 부족이 필요한 경우 장치를 향상 모드로 바이어스하여 + 2.5V의 최대 VGS에 대해 최대 20mA를 생성 할 수 있으며, 최소 출력 커패시턴스는 계속 핵심 요소입니다.

아래의 다음 애플리케이션은 적절한 향상 모드 전류 소스 회로를 보여줍니다.

예를 들어 테스트 도구의 자동 범위 지정 또는 스위치 ON시 논리 회로의 정확한 시작을 보장하기 위해 공급 전압 장애 중에 표준 조건이 필요한 요구 사항에 대해 '정상적으로 켜진'아날로그 스위치를 구축 할 수 있습니다.

장치의 감소 된 음의 임계 전압은 기본적인 드라이브 전제 조건을 제공하고 최소 전압으로 작업 할 수 있도록합니다.

아래 회로는 공핍 모드 DMOS 아날로그 스위치에 대한 공통 바이어스 요인을 보여줍니다.

장치가 꺼 지도록하려면 게이트에 음의 전압이 필요합니다. 즉, FET가 포지티브 게이트 전압을 사용하여 추가로 향상 될 때 온 저항이 최소화 될 수 있으며, 특히 공핍 모드 영역과 함께 향상 모드 영역에서 활성화됩니다.

이 응답은 다음 그래프에서 확인할 수 있습니다.

낮은 커패시턴스 값과 함께 장치의 고주파 이득은 향상된 '성능 지수'를 제공합니다. 이는 VHF 및 UHF 증폭에서 매우 중요한 요소로, FET의 이득 대역폭 곱 (GBW)을 지정하며 다음과 같이 표현할 수 있습니다.

GBW = gfs / 2 파이 (씨에+ C밖)

p 채널 공 핍형 MOSFET

p 채널 공 핍형 MOSFET의 구성은 그림 5.23에 표시된 n 채널 버전과 완전히 반대입니다. 즉, 아래 그림 5.28a에서 볼 수 있듯이 기판은 이제 n 유형의 형태를 취하고 채널은 p 유형이됩니다.

터미널 식별은 변경되지 않지만 동일한 그림에 표시된대로 전압과 전류 극성이 반전됩니다. 드레인 특성은 V를 제외하고 그림 5.25에 표시된 것과 똑같습니다.DS이 경우 음수 값을 얻는 부호.

드레인 전류 I디이 경우에도 양극성을 보여줍니다. 이는 이미 방향을 바꾸었기 때문입니다. VGS그림 5.28c에 표시된 것처럼 이해할 수있는 반대 극성을 보여줍니다.

V 때문에GS반전은 그림 5,28b에 표시된대로 전송 특성에 대한 미러 이미지를 생성합니다.

즉, 드레인 전류는 양의 V에서 증가합니다.GSV에서 컷오프 지점에서 영역GS= 나까지 VpDSS, V의 음수 값으로 계속 상승합니다.GS상승합니다.

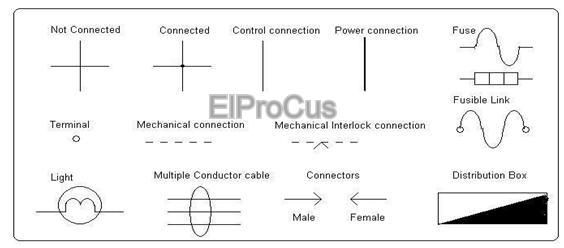

기호

n 채널 및 p 채널 공 핍형 MOSFET의 그래픽 신호는 위의 그림 5.29에서 확인할 수 있습니다.

선택한 기호가 장치의 실제 구조를 나타내는 것을 목표로하는 방식을 관찰하십시오.

게이트와 채널 사이에 직접 상호 연결 (게이트 절연으로 인해)이없는 것은 게이트와 심볼의 다른 단자 사이의 간격으로 표시됩니다.

채널을 나타내는 수직선은 드레인과 소스 사이에 부착되며 기판에 의해 '고정'됩니다.

위의 그림에서는 각 유형의 채널에 대해 두 그룹의 기호가 제공되어 일부 장치에서는 기판이 외부에서 액세스 할 수있는 반면 다른 장치에서는 보이지 않을 수 있다는 사실을 강조합니다.

MOSFET (Enhancement-Type)

공 핍형 및 강화 형 MOSFET은 내부 구조 및 기능 모드에서 비슷해 보이지만 특성은 상당히 다를 수 있습니다.

주요 차이점은 차단 동작을위한 게이트-소스 전압의 특정 레벨에 의존하는 드레인 전류입니다.

정확하게 n 채널 강화 형 MOSFET은 일반적으로 공 핍형 MOSFET에 영향을 줄 수있는 음전위 범위 대신 양의 게이트 / 소스 전압으로 작동 할 수 있습니다.

“변전소는 무엇입니까 ”

기본 구조

다음에서 n 채널 강화 형 MOSFET을 시각화 할 수 있습니다.

그림 5.31.

p- 타입 재료 섹션은 실리콘베이스를 통해 생성되며 이전에 배운대로 기판이라고합니다.

이 기판은 경우에 따라 공 핍형 MOSFET의 소스 핀으로 내부적으로 부착되는 반면, 경우에 따라 전위 레벨의 외부 제어를 가능하게하는 네 번째 리드로 종단됩니다.

소스 및 드레인 단자는 일반적으로 금속 접점을 사용하여 n- 도핑 영역에 결합됩니다.

그러나 그림 5.31에서 두 개의 n- 도핑 영역 사이의 채널이 누락되었음을 시각화하는 것이 중요 할 수 있습니다.

이것은 공 핍형과 강화 형 MOSFET의 내부 레이아웃 사이의 근본적인 차이점, 즉 장치의 일부로 간주되는 고유 채널이없는 것으로 간주 될 수 있습니다.

SiO2 층은 여전히 널리 퍼져있어 게이트 단자의 금속베이스와 드레인과 소스 사이의 영역 사이의 분리를 보장합니다. 그러나 여기서는 p 형 재료 섹션과 분리되어 서있는 것을 볼 수 있습니다.

위의 논의에서 우리는 고갈 및 강화 MOSFET 내부 레이아웃이 강화 유형의 MOSFET에 대한 드레인 / 소스 간의 누락 된 채널을 제외하고는 몇 가지 유사점을 가질 수 있다는 결론을 내릴 수 있습니다.

기본 작동 및 특성

향상 형 MOSFET의 경우 VGS에 0V가 도입되면 n 채널 (많은 자유 캐리어를 운반하는 것으로 알려져 있음)이 누락되어 전류 출력이 0이되며 이는 공 핍형과는 매우 다릅니다. ID = IDSS를 갖는 MOSFET의.

드레인 / 소스 단자를 가로 지르는 경로 누락으로 인해 이러한 상황에서 전자 형태의 많은 양의 캐리어는 (n- 도핑 된 영역으로 인해) 드레인 / 소스에 축적 될 수 없습니다.

VDS에서 약간의 포지티브 전위를 적용하고 VGS는 0V로 설정되고 SS 단자는 소스 단자와 단락 된 상태에서 실제로 n- 도핑 된 영역과 p- 기판 사이에 두 개의 역방향 바이어스 pn 접합을 발견하여 눈에 띄는 전도를 가능하게합니다. 소스로 배수하십시오.

그림 5.32는 VDS와 VGS가 0V보다 높은 양의 전압으로 적용되어 드레인과 게이트가 소스에 대해 양의 전위가 될 수있는 조건을 보여줍니다.

게이트의 포지티브 전위는 위 그림과 같이 SiO2 층의 가장자리를 따라 p 기판의 구멍을 밀어서 위치를 벗어나 p 기판 영역으로 더 깊숙이 들어가게합니다. 이것은 서로를 격퇴하는 유사한 요금 때문에 발생합니다.

그 결과, 공극이없는 SiO2 절연 층 가까이에 공핍 영역이 생성됩니다.

그럼에도 불구하고 재료의 소수 캐리어 인 p- 기판 전자는 포지티브 게이트를 향해 당겨져 SiO2 층 표면에 가까운 영역에서 모이기 시작합니다.

SiO2 층의 절연 특성으로 인해 음극 캐리어는 음극 캐리어가 게이트 단자에서 흡수되는 것을 방지합니다.

VGS의 수준을 높이면 SiO2 표면에 가까운 전자 밀도도 증가하여 마침내 유도 된 n 형 영역이 드레인 / 소스를 가로 질러 정량화 가능한 전도를 허용 할 수 있습니다.

드레인 전류를 최적으로 증가시키는 VGS 크기를 임계 전압이라고합니다. VT 기호로 표시 . 데이터 시트에서이를 VGS (Th)로 볼 수 있습니다.

위에서 배운 바와 같이 VGS = 0에서 채널이없고 양의 게이트-소스 전압 애플리케이션으로 '향상'된이 유형의 MOSFET을 향상 형 MOSFET이라고합니다.

공 핍형 및 향상 형 MOSFET 모두 향상 형 영역을 나타내지 만 상승 특히 향상된 작동 모드를 사용하여 작동하기 때문에 후자에 사용됩니다.

이제 VGS가 임계 값 이상으로 밀릴 때 자유 캐리어의 농도는 유도되는 채널에서 증가합니다. 이로 인해 드레인 전류가 증가합니다.

반면에 VGS를 일정하게 유지하고 VDS (드레인-소스 전압) 레벨을 높이면 일반적으로 JFET 또는 공핍 MOSFET에서도 발생하는 것처럼 MOSFET이 포화 지점에 도달하게됩니다.

그림 5.33에서 볼 수 있듯이 드레인 전류 ID는 유도 된 채널의 드레인 끝쪽으로가는 좁은 채널로 표시되는 핀칭 오프 프로세스의 도움으로 평준화됩니다.

Kirchhoff의 전압 법칙을 그림 5.33에서 MOSFET의 단자 전압에 적용하면 다음과 같은 결과를 얻을 수 있습니다.

VGS가 특정 값 (예 : 8V)으로 일정하게 유지되고 VDS가 2V에서 5V로 상승하면 전압 VDG는 Eq. 5.11은 -6V에서 -3V로 떨어지고 게이트 전위는 드레인 전압에 대해 점점 더 적은 양이되는 것을 볼 수 있습니다.

이 반응은 자유 캐리어 또는 전자가 유도 된 채널의이 영역으로 당겨지는 것을 방지하며, 결과적으로 채널의 유효 폭이 감소합니다.

궁극적으로 채널 폭은 pinch-off 지점까지 감소하여 이전 공핍 MOSFET 기사에서 이미 배운 것과 유사한 포화 조건에 도달합니다.

즉, 고정 VGS로 VDS를 더 높이면 고장 상황에 도달 할 때까지 ID의 포화 수준에 영향을주지 않습니다.

그림 5.34를 보면 VGS = 8V 인 그림 5.33에서와 같은 MOSFET의 경우 VDS 레벨 6V에서 포화가 발생 함을 확인할 수 있습니다. 정확하게 VDS 포화 레벨은 다음과 같은 방법으로 적용된 VGS 레벨과 연관됩니다.

의심 할 여지없이 VT 값이 고정 될 때 VGS 수준을 높이면 포화 수준의 궤적을 통해 VDS에 대한 포화 수준이 비례 적으로 높아진다는 것을 의미합니다.

위 그림에 표시된 특성을 참조하면 VT 레벨은 2V이며, 이는 드레인 전류가 0mA로 떨어 졌다는 사실에서 알 수 있습니다.

따라서 일반적으로 다음과 같이 말할 수 있습니다.

VGS 값이 향상 형 MOSFET의 임계 값 수준보다 작 으면 드레인 전류는 0mA입니다.

또한 위의 그림에서 VGS가 VT에서 8V로 높아지면 ID에 대한 해당 포화 수준도 0에서 10mA 수준으로 증가한다는 것을 분명히 알 수 있습니다.

또한 VGS 값이 증가함에 따라 VGS 레벨 사이의 공간이 증가하여 드레인 전류가 무한히 증가 함을 알 수 있습니다.

드레인 전류 값은 다음과 같은 비선형 관계를 통해 VT보다 큰 VGS 레벨의 게이트-소스 전압과 관련이 있습니다.

대괄호로 표시된 용어는 ID와 VGS 간의 비선형 관계를 담당하는 용어입니다.

용어 k는 상수이며 MOSFET 레이아웃의 기능입니다.

다음 방정식을 통해이 상수 k의 값을 찾을 수 있습니다.

여기서 ID (on) 및 VGD (on)는 각각 장치의 특성에 따른 값입니다.

아래의 그림 5.35에서 우리는 드레인과 전송 특성이 서로 나란히 배열되어있는 것을 볼 수 있습니다.

기본적으로 JFET 및 공 핍형 MOSFET에 대해 이전에 설명한 프로세스와 유사합니다.

그러나 현재의 경우 VGS VT의 경우 드레인 전류가 0mA임을 기억해야합니다.

여기서 ID는 눈에 띄는 양의 전류를 볼 수 있으며, 이는 식에 의해 결정됩니다. 5.13.

드레인 특성에서 전달 특성에 대한 포인트를 정의하는 동안 포화 수준 만 고려합니다. 이는 작동 영역을 식에 의해 설정된 포화 수준보다 높은 VDS 값으로 제한합니다. (5.12).

p 채널 향상 형 MOSFET

그림 5.37a에 표시된 p 채널 향상 형 MOSFET의 구조는 그림 5.31에 표시된 것과 정반대입니다.

즉, 이제 드레인 및 소스 조인트 아래에 n 형 기판과 p- 도핑 영역이 있음을 알 수 있습니다.

단자는 계속 설정되어 있지만 각 전류 방향과 전압 극성이 반대입니다.

드레인 특성은 그림 5.37c에서와 같이 지속적으로 더 많은 음의 크기의 VGS로 인해 전류량이 증가하는 것처럼 보일 수 있습니다.

전송 특성은 그림 5.37b에 표시된대로 VT보다 VGS의 음의 값이 점점 더 증가함에 따라 ID가 증가하는 그림 5.35의 전송 곡선의 거울 인상 (ID 축 주변)입니다. 방정식 (5.11) ~ (5.14)는 p- 채널 장치에도 유사하게 적합합니다.

참조 :

- https://en.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4%AE%E0%A5%89%E0%A4%B8%E0%A4%AB%E0%A5%87%E0%A4%9F

이전 : 안티 스파이 RF 감지기 회로 – 무선 버그 감지기 다음 : 전송 특성

![점접점 다이오드 [연혁, 구성, 응용회로]](https://electronics.jf-parede.pt/img/electronics-tutorial/38/point-contact-diodes-history-construction-application-circuit-1.jpg)