결과적으로 프로그램 실행 속도를 높이면 프로세서. 실행 속도를 높이기 위해 하드웨어 구현과 소프트웨어 아키텍처 모두에서 여러 가지 방법이 발명되었습니다. 명령을 동시에 실행함으로써 실행에 필요한 시간을 줄일 수 있음이 관찰되었습니다. 병렬화의 개념 프로그램 작성 제안되었습니다. 이에 따라 클럭 사이클 당 하나 이상의 명령을 실행할 수 있습니다. 이 개념은 프로그래머가 다음과 같은 다양한 기술을 통해 실행할 수 있습니다. 파이프 라이닝, 다중 실행 단위 및 다중 코어 . 이러한 모든 병렬 처리 방법 중에서 파이프 라이닝이 가장 일반적으로 실행됩니다. 그렇다면 파이프 라이닝 메서드에서 명령을 어떻게 실행할 수 있습니까? 실행 속도를 어떻게 증가 시킵니까?

파이프 라이닝이란?

파이프 라이닝의 개념을 이해하기 위해 프로그램 실행 방법의 루트 수준을 살펴 보겠습니다. 명령어는 프로그램의 가장 작은 실행 패킷입니다. 각 명령어에는 하나 이상의 작업이 포함됩니다. 단순 스칼라 프로세서는 클럭주기 당 하나 이상의 명령어를 실행하며 각 명령어는 하나의 연산 만 포함합니다. 명령은 예상 결과를 생성하기 위해 일련의 단계로 실행됩니다. 이 순서는 아래와 같습니다.

명령어 실행 순서

- IF : 명령어를 명령어 레지스터로 가져옵니다.

- ID : Instruction Decode, opcode에 대한 명령을 디코딩합니다.

- AG : 주소 생성기, 주소를 생성합니다.

- DF : 데이터 페치, 피연산자를 데이터 레지스터로 페치합니다.

- EX : 실행, 지정된 작업을 실행합니다.

- WB : 다시 쓰기, 결과를 다시 쓰기 레지스터.

모든 지침에 위의 모든 단계가 필요한 것은 아니지만 대부분은 필요합니다. 이 단계는 다른 하드웨어 기능을 사용합니다. 파이프 라이닝에서는 이러한 여러 단계가 동시에 수행됩니다. 파이프 라이닝에서 이러한 단계는 서로 다른 작업간에 독립적으로 간주되며 겹칠 수 있습니다. 따라서 여러 작업을 동시에 수행 할 수 있으며 각 작업은 독립적 인 단계에 있습니다.

명령 파이프 라이닝

파이프 라이닝에서 명령어가 처리되는 방식을 살펴 보겠습니다. 이것은 아래 다이어그램을 통해 쉽게 이해할 수 있습니다.

명령 파이프 라이닝

명령어가 독립적이라고 가정합니다. 단순 파이프 라이닝 프로세서에서는 주어진 시간에 각 단계에서 하나의 작업 만 있습니다. 초기 단계는 IF 단계입니다. 따라서 첫 번째 클록 사이클에서 하나의 작업이 페치됩니다. 다음 클럭 펄스가 도착하면 첫 번째 작업이 ID 단계로 이동하여 IF 단계를 비워 둡니다. 이제이 빈 단계가 다음 작업에 할당됩니다. 따라서 두 번째 클럭 펄스 동안 첫 번째 작업은 ID 단계에 있고 두 번째 작업은 IF 단계에 있습니다.

세 번째 사이클의 경우 첫 번째 작업은 AG 단계에 있고 두 번째 작업은 ID 단계에 있으며 세 번째 작업은 IF 단계에 있습니다. 이러한 방식으로 명령이 동시에 실행되고 6주기 후에 프로세서는 클럭주기 당 완전히 실행 된 명령을 출력합니다.

이 명령어가 순차적으로 실행 되었습니까? 처음에 첫 번째 명령어가 모든 단계를 거쳐야하고 다음 명령어가 페치됩니까? 따라서 각 명령을 실행하려면 프로세서에 6 개의 클럭 사이클이 필요합니다. 그러나 파이프 라인 프로세서에서는 명령어 실행이 동시에 발생하기 때문에 초기 명령어 만 6 사이클이 필요하고 나머지 모든 명령어는 각 사이클 당 하나씩 실행되므로 실행 시간이 단축되고 프로세서 속도가 증가합니다.

파이프 라이닝 아키텍처

병렬화는 하드웨어, 컴파일러 및 소프트웨어 기술로 달성 할 수 있습니다. 파이프 라이닝의 개념을 활용하려면 컴퓨터 아키텍처 많은 프로세서 장치가 상호 연결되어 동시에 작동합니다. 파이프 라인 프로세서 아키텍처에는 정수 및 부동 소수점 명령어를 위해 제공되는 별도의 처리 장치가 있습니다. 순차 아키텍처에서는 단일 기능 단위가 제공됩니다.

파이프 라인 프로세서 유닛

정적 파이프 라이닝에서 프로세서는 명령 요구 사항에 관계없이 파이프 라인의 모든 단계를 통해 명령을 전달해야합니다. 동적 파이프 라인 프로세서에서 명령은 요구 사항에 따라 단계를 우회 할 수 있지만 순차적으로 이동해야합니다. 복잡한 동적 파이프 라인 프로세서에서 명령어는 단계를 우회하고 순서가 잘못된 단계를 선택할 수 있습니다.

RISC 프로세서의 파이프 라이닝

가장 인기있는 RISC 아키텍처 ARM 프로세서는 3 단계 및 5 단계 파이프 라이닝을 따릅니다. 3 단계 파이프 라이닝에서 단계는 가져 오기, 디코딩 및 실행입니다. 이 파이프 라이닝은 개별 명령어가 완료되는 데 3 클럭주기가 걸리므로 3주기의 대기 시간이 있습니다.

ARM 3 단계 파이프 라이닝

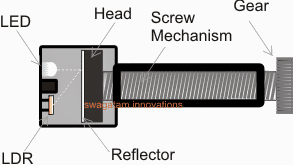

파이프 라이닝의 적절한 구현을 위해 하드웨어 아키텍처도 업그레이드해야합니다. 3 단계 파이프 라이닝을위한 하드웨어에는 레지스터 뱅크, ALU, 배럴 시프터, 주소 생성기, 증 분기, 명령어 디코더 및 데이터 레지스터가 포함됩니다.

ARM 3 단계 파이프 라이닝 데이터 경로

파이프 라이닝 5 단계에서 단계는 가져 오기, 디코딩, 실행, 버퍼 / 데이터 및 쓰기입니다.

파이프 라이닝 위험

일반적인 컴퓨터 프로그램에는 간단한 명령어 외에 분기 명령어, 인터럽트 연산, 읽기 및 쓰기 명령어가 있습니다. 파이프 라이닝은 모든 종류의 지침에 적합하지 않습니다. 파이프 라이닝에서 일부 명령이 실행되면 파이프 라인을 중단하거나 완전히 플러시 할 수 있습니다. 파이프 라이닝 중에 발생하는 이러한 유형의 문제를 파이프 라이닝 위험이라고합니다.

대부분의 컴퓨터 프로그램에서 한 명령어의 결과는 다른 명령어의 피연산자로 사용됩니다. 이러한 명령어가 파이프 라이닝에서 실행되면 명령어 2가 피연산자 수집을 시작할 때 첫 번째 명령어의 결과를 사용할 수 없으므로 브레이크 다운이 발생합니다. 따라서 명령 2는 명령 1이 실행되고 결과가 생성 될 때까지 중단되어야합니다. 이러한 유형의 위험을 Read –after-write 파이프 라이닝 위험이라고합니다.

쓰기 후 읽기 파이프 라이닝 위험

분기 명령을 실행하면 파이프 라이닝 위험도 발생합니다. 실행 중 분기 명령 파이프 라이닝 다음 지침의 가져 오기 단계에 영향을줍니다.

파이프 라인 분기 동작

파이프 라이닝의 장점

- 명령 처리량이 증가합니다.

- 파이프 라인 단계 수가 증가하면 동시에 실행되는 명령 수가 증가합니다.

- 파이프 라이닝을 사용할 때 더 빠른 ALU를 설계 할 수 있습니다.

- 파이프 라인 CPU는 RAM보다 높은 클럭 주파수에서 작동합니다.

- 파이프 라이닝은 CPU의 전반적인 성능을 향상시킵니다.

파이프 라이닝의 단점

- 파이프 라인 프로세서의 설계는 복잡합니다.

- 파이프 라인 프로세서에서 명령어 지연 시간이 증가합니다.

- 파이프 라인 프로세서의 처리량은 예측하기 어렵습니다.

- 파이프 라인이 길수록 분기 지침에 대한 위험 문제가 악화됩니다.

파이프 라이닝은 유사한 실행 단계를 따르는 모든 명령에 도움이됩니다. 모든 명령어가 다른 명령어와 다르게 동작하는 복잡한 명령어가있는 프로세서는 파이프 라인이 어렵습니다. 프로세서는 파이프 라인의 깊이가 증가함에 따라 관련 위험이 증가하기 때문에 파이프 라인의 3 ~ 5 단계로 합리적인 구현을 가지고 있습니다. 파이프 라인 단계와 함께 파이프 라인 된 프로세서의 이름을 지정 하시겠습니까?