에 디지털 전자 2 비트 이진수 추가는 다음을 사용하여 가능합니다. 반가산기 . 그리고 입력 시퀀스가 3 비트 시퀀스 인 경우 전체 가산기를 사용하여 추가 프로세스를 완료 할 수 있습니다. 그러나 입력 시퀀스에서 비트 수가 더 많으면 반가산기를 사용하여 프로세스를 완료 할 수 있습니다. 전체 가산기는 추가 작업을 완료 할 수 없기 때문입니다. 따라서 이러한 단점은 'Ripple Carry Adder'를 사용하여 극복 할 수 있습니다. 독특한 유형의 논리 회로 디지털 연산에서 N 비트 숫자를 추가하는 데 사용됩니다. 이 기사에서는 리플 캐리 가산기 및 그 작동에 대한 개요를 설명합니다.

Ripple Carry Adder는 무엇입니까?

다중 완전 가산기의 구조는 n 비트 이진 시퀀스의 추가 결과를 제공하는 방식으로 계단식으로 연결됩니다. 이 가산기는 구조에 캐스케이드 된 완전 가산기를 포함하므로 리플 운반 가산기 회로의 모든 완전 가산기 단계에서 캐리가 생성됩니다. 각 완전 가산기 단계에서 이러한 캐리 출력은 다음 완전 가산기로 전달되고 거기에 캐리 입력으로 적용됩니다. 이 프로세스는 마지막 전체 가산기 단계까지 계속됩니다. 따라서 각 캐리 출력 비트는 전체 가산기의 다음 단계로 리플 링됩니다. 이 때문에“RIPPLE CARRY ADDER”로 명명됩니다. 그것의 가장 중요한 특징은 시퀀스가 4 비트이든 5 비트이든 어떤 것이 든 입력 비트 시퀀스를 추가하는 것입니다.

“이 캐리 가산기에서 고려해야 할 가장 중요한 점 중 하나는 캐리 출력이 각 풀 가산기 단계에서 생성되고 다음 단계로 전달 된 후에 만 최종 출력이 알려진다는 것입니다. 따라서이 캐리 가산기를 사용하여 결과를 얻는 데 지연이있을 것입니다.”

리플 운반 가산기에는 다양한 유형이 있습니다. 그들은:

- 4 비트 리플 캐리 가산기

- 8 비트 리플 캐리 가산기

- 16 비트 리플 캐리 가산기

먼저 4 비트 리플 캐리 가산기로 시작한 다음 8 비트 및 16 비트 리플 캐리 가산기로 시작합니다.

4 비트 리플 캐리 가산기

아래 다이어그램은 4 비트 리플 캐리 가산기를 나타냅니다. 이 가산기에서는 4 개의 완전 가산기가 캐스케이드로 연결됩니다. Co는 캐리 입력 비트이며 항상 0입니다. 이 입력 캐리 'Co'가 두 개의 입력 시퀀스 A1 A2 A3 A4 및 B1 B2 B3 B4에 적용되면 출력은 S1 S2 S3 S4로 표시되고 출력은 C4를 전달합니다.

4 비트 RCA 다이어그램

4 비트 리플 캐리 가산기 작동

- 두 개의 입력 시퀀스 0101 및 1010의 예를 들어 보겠습니다. 이들은 A4 A3 A2 A1 및 B4 B3 B2 B1을 나타냅니다.

- 이 가산기 개념에 따라 입력 캐리는 0입니다.

- Ao & Bo가 입력과 함께 첫 번째 완전 가산기에 적용될 때 0을 전달합니다.

- 여기서 A1 = 1 B1 = 0 Cin = 0

- 합계 (S1) 및 캐리 (C1)는이 가산기의 합계 및 캐리 방정식에 따라 생성됩니다. 이론에 따라 Sum = A1⊕B1⊕Cin 및 Carry = A1B1⊕B1Cin⊕CinA1의 출력 방정식

- 이 방정식에 따라 첫 번째 완전 가산기 S1 = 1 및 Carry 출력 즉, C1 = 0입니다.

- 다음 입력 비트 A2 및 B2, 출력 S2 = 1 및 C2 = 0과 동일합니다. 여기서 중요한 점은 두 번째 단계 완전 가산기가 입력 캐리를 얻는다는 것입니다. 즉, 초기 단계 완전 가산기의 출력 캐리 인 C1입니다.

- 이와 같이 최종 출력 시퀀스 (S4 S3 S2 S1) = (111 1) 및 출력 캐리 C4 = 0을 얻습니다.

- 이 캐리 가산기에 적용될 때 4 비트 입력 시퀀스에 대한 추가 프로세스입니다.

8 비트 리플 캐리 가산기

- 계단식으로 연결된 8 개의 완전 가산기로 구성됩니다.

- 각 전체 가산기 캐리 출력은 다음 단계 전체 가산기에 대한 입력 캐리로 연결됩니다.

- 입력 시퀀스는 (A1 A2 A3 A4 A5 A6 A7 A8) 및 (B1 B2 B3 B4 B5 B6 B7 B8)로 표시되며 관련 출력 시퀀스는 (S1 S2 S3 S4 S5 S6 S7 S8)로 표시됩니다.

- 8 비트 리플-캐리-가산기에서 추가 프로세스는 4 비트 리플-캐리-가산기에서 사용되는 것과 동일한 원리입니다. 즉, 두 입력 시퀀스의 각 비트가 입력 캐리와 함께 추가됩니다.

- 이것은 두 개의 8 비트 이진수 시퀀스를 추가 할 때 사용됩니다.

8 비트 리플 캐리 가산기

16 비트 리플 캐리 가산기

- 그것은 계단식 형태로 연결된 16 개의 완전 가산기로 구성됩니다.

- 각 전체 가산기 캐리 출력은 다음 단계 전체 가산기에 대한 입력 캐리로 연결됩니다.

- 입력 시퀀스는 (A1… .. A16) 및 (B1 …… B16)으로 표시되고 관련 출력 시퀀스는 (S1 …… .. S16)으로 표시됩니다.

- 16 비트 리플-캐리-가산기의 추가 프로세스는 4 비트 리플-캐리-가산기에서 사용되는 것과 동일한 원리입니다. 즉, 두 입력 시퀀스의 각 비트가 입력 캐리와 함께 추가됩니다.

- 두 개의 16 비트 이진수 시퀀스를 추가 할 때 사용합니다.

16 비트 리플 캐리 가산기

리플 캐리 가산기 진실 표

아래 진리표는 ripple-carry-adder에 대한 모든 입력의 가능한 조합에 대한 출력 값을 보여줍니다.

| A1 | A2 | A3 | A4 | B4 | B3 | B2 | B1 | S4 | S3 | S2 | S1 | 나르다 |

0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

리플 캐리 가산기 VHDL 코드

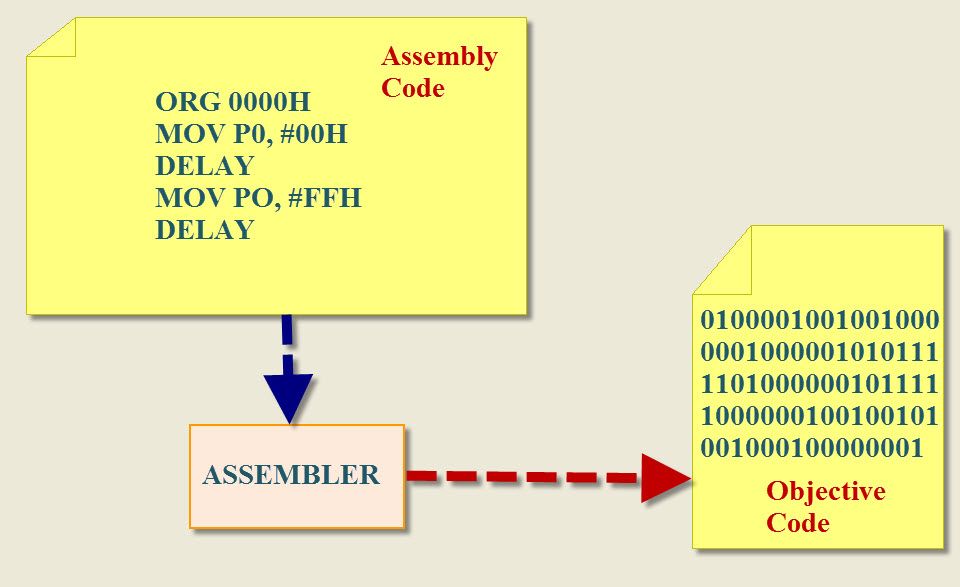

VHDL (VHSIC HDL)은 하드웨어 설명 언어입니다. 디지털 디자인 언어입니다. 이 캐리 가산기의 VHDL 코드는 다음과 같습니다.

도서관 IEEE

IEEE.STD_LOGIC_1164.ALL 사용

엔티티 Ripplecarryadder는

포트 (A : STD_LOGIC_VECTOR (3에서 0까지)

B : STD_LOGIC_VECTOR (3에서 0까지)

Cin : STD_LOGIC에서

S : STD_LOGIC_VECTOR 출력 (3에서 0까지)

Cout : 출력 STD_LOGIC)

끝 Ripplecarryadder

Ripplecarryadder의 아키텍처 동작은 다음과 같습니다. — Full Adder VHDL 코드 구성 요소 선언

구성 요소 full_adder_vhdl_code

포트 (A : STD_LOGIC

B : STD_LOGIC에서

Cin : STD_LOGIC에서

S : STD_LOGIC 출력

Cout : 출력 STD_LOGIC)

끝 구성 요소

— 중급 캐리 선언

신호 c1, c2, c3 : STD_LOGIC

시작하다

— Port Mapping Full Adder 4 회

FA1 : full_adder_vhdl_code 포트 맵 (A (0), B (0), Cin, S (0), c1)

FA2 : full_adder_vhdl_code 포트 맵 (A (1), B (1), c1, S (1), c2)

FA3 : full_adder_vhdl_code 포트 맵 (A (2), B (2), c2, S (2), c3)

FA4 : full_adder_vhdl_code 포트 맵 (A (3), B (3), c3, S (3), Cout)

행동 종료

리플 캐리 가산기 Verilog 코드

Verilog 코드는 하드웨어 설명 언어입니다. 설계 및 검증 목적으로 RTL 단계의 디지털 회로에 사용됩니다. 이 캐리 가산기의 verilog 코드는 다음과 같습니다.

모듈 ripple_carry_adder (a, b, cin, sum, cout)

입력 [03 : 0] a

입력 [03 : 0] b

입력 cin

출력 [03 : 0] 합계

출력 cout

와이어 [2 : 0] c

fulladd a1 (a [0], b [0], cin, sum [0], c [0])

fulladd a2 (a [1], b [1], c [0], sum [1], c [1])

fulladd a3 (a [2], b [2], c [1], sum [2], c [2])

fulladd a4 (a [3], b [3], c [2], sum [3], cout)

endmodule

fulladd 모듈 (A, B, CIN, 합계 COUT)

입력 a, b, cin

출력 합계, cout

할당 합계 = (a ^ b ^ cin)

할당 cout = ((a & b) | (b & cin) | (a & cin))

리플 캐리 가산기 애플리케이션

리플 운반 가산기 애플리케이션에는 다음이 포함됩니다.

- 이러한 캐리 가산기는 주로 n 비트 입력 시퀀스와 함께 사용됩니다.

- 이러한 캐리 가산기는 디지털 신호 처리 및 마이크로 프로세서 .

리플 캐리 가산기 장점

리플 캐리 가산기의 장점은 다음과 같습니다.

- 이 캐리 가산기는 정확한 결과를 얻기 위해 n- 비트 시퀀스에 대한 가산 처리를 수행 할 수있는 것과 같은 장점이 있습니다.

- 이 가산기의 설계는 복잡한 과정이 아닙니다.

리플 캐리 가산기 반가산기 및 전 가산기가 입력 비트 시퀀스가 클 때 더하기 연산을 수행하지 않는 경우에 대한 대안입니다. 그러나 여기서는 약간의 지연이있는 입력 비트 시퀀스에 대한 출력을 제공합니다. 디지털 회로에 따라 회로가 출력을 지연 시키면 바람직하지 않습니다. 이것은 캐리 예견 가산기 회로로 극복 할 수 있습니다.

![4 개의 간단한 박수 스위치 회로 [테스트 됨]](https://electronics.jf-parede.pt/img/4017-ic-circuits/21/4-simple-clap-switch-circuits.png)