이 게시물에서는 개별 트랜지스터를 사용하여 NOT, AND, NAND, OR 및 NOR 논리 게이트를 만드는 방법을 배웁니다. 트랜지스터 논리 게이트를 사용하는 주요 이점은 1.5V의 낮은 전압에서도 작동할 수 있다는 것입니다.

일부 전자 애플리케이션에서는 사용 가능한 전압이 TTL 또는 CMOS IC에 전원을 공급하기에 부적절할 수 있습니다. 이것은 배터리로 작동하는 가제트에 특히 해당됩니다. 의심할 여지 없이 항상 3볼트 로직 IC 옵션이 있습니다. 그러나 이들은 애호가나 실험자가 항상 쉽게 액세스할 수 있는 것은 아니며 정의된 전압 사양(일반적으로 2.5V DC 미만) 아래에서 작동하지 않습니다.

또한 배터리 구동 애플리케이션에서는 단일 1.5볼트 배터리만 있을 수 있습니다. 자, 그럼 어떻게 하실 건가요? 대개 IC 논리 게이트 트랜지스터화된 논리 게이트로 대체될 수 있습니다. 각 특정 논리 게이트에는 일반적으로 몇 개의 트랜지스터만 필요하고 일반적인 NOT 게이트 인버터 논리에는 하나의 트랜지스터만 필요합니다.

FET 대 바이폴라 트랜지스터

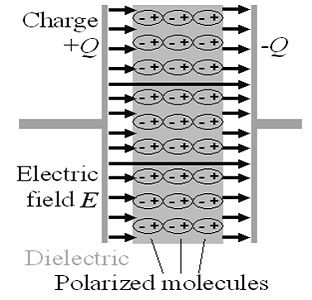

전계 효과 트랜지스터(FET) 대 바이폴라 트랜지스터 : 저전압 논리 회로에 대한 더 나은 옵션은 무엇입니까? 의 훌륭한 기능 중 하나는 사리 그들의 '온' 저항이 엄청나게 낮다는 것입니다. 또한 매우 낮은 게이트 턴온 전류가 필요합니다.

그러나 초저전압 애플리케이션에서는 한 가지 제한이 있습니다. 일반적으로 게이트 전압 제한은 1볼트 정도입니다. 또한 전류 제한 또는 풀다운 저항이 게이트에 부착된 경우 사용 가능한 전압이 FET의 최적 작동 범위 아래로 감소할 수 있습니다.

반대로 바이폴라 스위칭 트랜지스터는 0.6~0.7볼트만 켜면 켜지기 때문에 극도로 낮은 전압의 단일 배터리 애플리케이션에서 이점이 있습니다.

또한 가장 가까운 전자 제품 매장에서 일반적으로 버블 팩으로 판매되는 대부분의 일반 FET는 바이폴라 트랜지스터보다 더 비쌉니다. 또한, 바이폴라 트랜지스터의 벌크 패킷은 일반적으로 한 쌍의 FET 가격으로 구입할 수 있습니다.

FET 핸들링은 바이폴라 트랜지스터 핸들링보다 훨씬 더 많은 주의가 필요합니다. 정전기 및 일반적인 실험 오용으로 인해 FET가 특히 손상되기 쉽습니다. 번트 구성 요소는 디버깅의 정서적 고통을 잊지 않기 위해 실험이나 혁신의 즐겁고 창의적인 저녁을 망칠 수 있습니다.

스위칭 트랜지스터의 기본

이 기사에서 설명하는 논리 회로 예제에서는 바이폴라 NPN 트랜지스터가 저렴하고 특별한 처리가 필요하지 않기 때문에 사용합니다. 장치 또는 이를 지원하는 부품의 손상을 방지하려면 회로를 연결하기 전에 적절한 안전 조치를 취해야 합니다.

우리 회로가 주로 BJT(Bipolar Junction Transistors)에 집중되어 있지만 FET 기술을 사용하여 똑같이 잘 구성할 수 있었습니다.

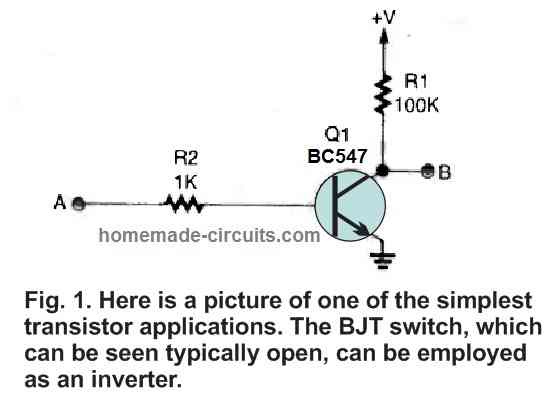

기본 스위치 회로는 가장 쉬운 설계 중 하나인 간단한 트랜지스터 응용 프로그램입니다.

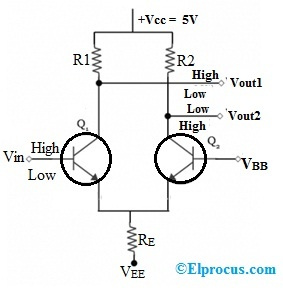

단일 트랜지스터로 NOT 게이트 만들기

트랜지스터 스위치의 개략도는 그림 1에 나와 있습니다. 특정 애플리케이션에서 구현하는 방법에 따라 스위치는 낮게 유지되거나 정상적으로 열린 상태로 표시될 수 있습니다.

간단한 NOT 게이트 인버터 논리 게이트는 그림 1(여기서 점 A는 입력)에 표시된 간단한 스위칭 회로로 생성할 수 있습니다. NOT 게이트는 트랜지스터의 베이스(포인트 A, Q1)에 DC 바이어스가 제공되지 않으면 차단 상태를 유지하여 출력에서 하이 또는 로직 1(V+ 레벨과 동일)이 되는 방식으로 작동합니다. 포인트 B).

그러나 트랜지스터는 Q1의 베이스에 적절한 바이어스가 제공될 때 활성화되어 회로의 출력을 로우 또는 로직 0(거의 제로 전위와 동일)으로 푸시합니다. Q1으로 지정된 트랜지스터는 범용 바이폴라 트랜지스터 또는 BC547이며 일반적으로 저전력 스위칭 및 증폭기 애플리케이션에 사용됩니다.

이에 상응하는 모든 트랜지스터(예: 2N2222, 2N4401 등)가 작동합니다. R1 및 R2의 값은 낮은 전류 드레인과 호환성 사이의 절충점을 찾기 위해 선택되었습니다. 모든 설계에서 저항은 모두 1/4와트, 5% 단위입니다.

공급 전압은 1.4~6V DC 사이에서 조정 가능합니다. 회로는 부하 저항과 출력 연결이 트랜지스터의 이미 터로 이동될 때 버퍼처럼 작동할 수 있습니다.

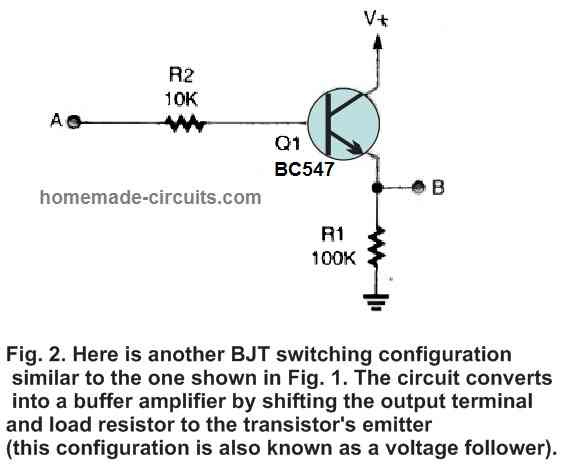

단일 BC547 BJT를 사용하여 버퍼 게이트 만들기

전압 팔로워 또는 버퍼 증폭기는 그림 2에 표시된 것과 동일한 유형의 논리 스위칭 구성입니다. 이 회로에서 부하 저항과 출력 단자가 트랜지스터의 컬렉터에서 이미 터로 이동되었다는 점에 유의해야 합니다. 이 디자인과 그림 1에 표시된 디자인의 주요 차이점.

트랜지스터의 기능은 부하 저항과 출력 단자를 BJT의 다른 쪽 끝으로 이동하여 '반전'될 수도 있습니다.

즉, 회로의 입력에 바이어스가 제공되지 않으면 회로의 출력이 낮게 유지됩니다. 그러나 적절한 전압의 바이어스가 회로의 입력에 공급되면 회로의 출력이 높아집니다. (이것은 이전 회로에서 발생하는 것과 정확히 반대입니다.)

트랜지스터를 사용한 2입력 논리 게이트 설계

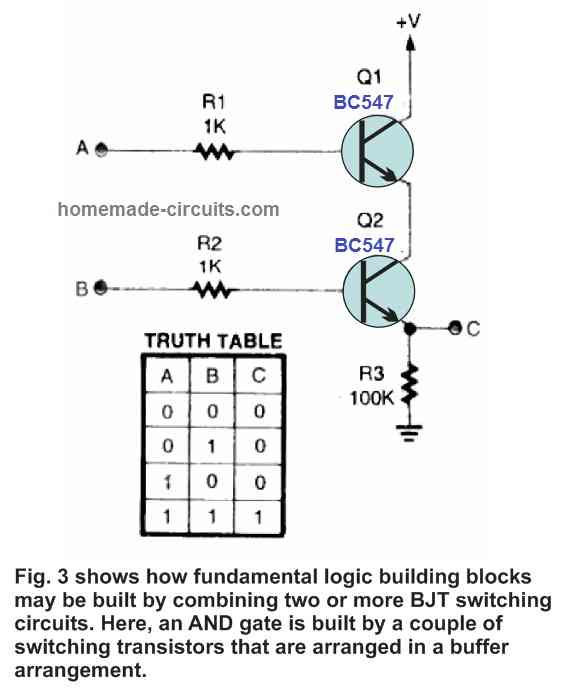

두 개의 트랜지스터를 사용한 AND 게이트

그림 3은 기본 2입력 AND 게이트가 해당 게이트에 대한 진리표와 함께 한 쌍의 버퍼를 사용하여 생성되는 방법을 보여줍니다. 진리표는 개별 입력 세트에 대한 출력 결과가 무엇인지 보여줍니다. 점 A와 B는 회로의 입력으로 사용되고 점 C는 회로의 출력으로 사용됩니다.

진리표에서 한 세트의 입력 매개변수만 로직 하이 출력 신호를 생성하는 반면, 다른 모든 입력 조합은 로직 로우 출력을 생성한다는 사실에 주목하는 것이 중요합니다. 그림 3의 AND 게이트 출력은 일단 하이로 바뀌면 V+보다 약간 낮게 유지됩니다.

이것은 두 트랜지스터(Q1 및 Q2) 사이의 전압 강하 때문에 발생합니다.

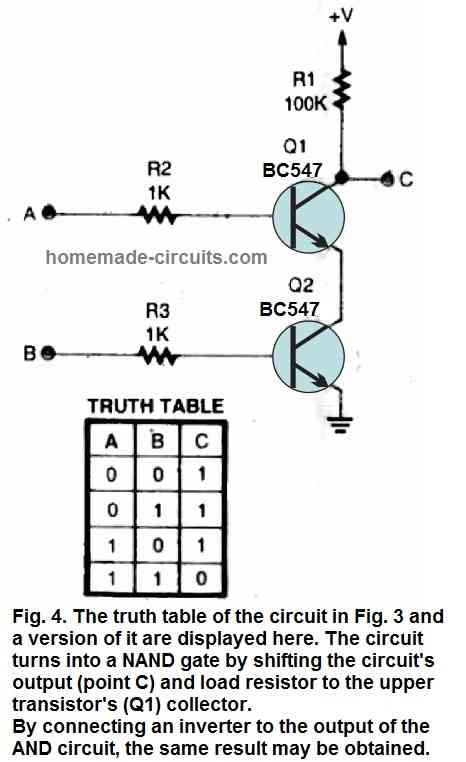

두 개의 트랜지스터를 사용하는 NAND 게이트

그림 3에 있는 회로의 또 다른 변형과 관련 진리표가 그림 4에 나와 있습니다. 이 회로는 출력(포인트 C)과 출력 저항을 상위 트랜지스터(Q1) 컬렉터로 이동하여 NAND 게이트로 바뀝니다.

R1의 낮은 쪽을 접지로 풀하려면 Q1과 Q2를 모두 ON으로 전환해야 하므로 출력 C에서의 전압 손실은 미미합니다.

트랜지스터 AND 또는 트랜지스터 NAND 게이트에 2개 이상의 입력이 필요한 경우 표시된 설계에서 더 많은 트랜지스터를 연결하여 3개, 4개 등의 입력 AND 또는 NAND 게이트를 제공할 수 있습니다.

그러나 개별 트랜지스터의 전압 손실을 보상하기 위해 V+를 상응하게 증가시켜야 합니다.

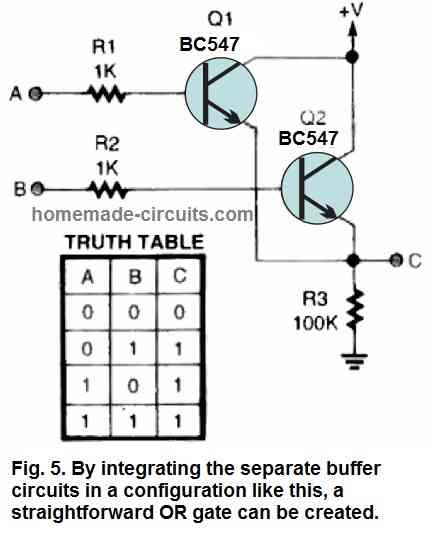

두 개의 트랜지스터를 사용하는 OR 게이트

두 개의 입력이 있는 논리 회로의 다른 형태는 OR 게이트 회로의 진리표와 함께 그림 5에서 볼 수 있습니다.

회로의 출력은 입력 A 또는 입력 B가 하이로 푸시될 때 높지만 캐스케이드된 트랜지스터로 인해 전압 강하는 0.5볼트 이상입니다. 그러나 표시된 수치는 후속 트랜지스터 게이트를 작동하기에 충분한 전압과 전류가 있음을 나타냅니다.

2개의 트랜지스터를 사용하는 NOR 게이트

그림 6은 목록의 다음 게이트인 2입력 NOR 게이트와 진리표를 보여줍니다. AND 및 NAND 게이트가 서로 응답하는 방식과 유사하게 OR 및 NOR 회로도 동일합니다.

표시된 각 게이트는 하나 이상의 인접한 트랜지스터 게이트를 활성화하기에 충분한 드라이브를 공급할 수 있습니다.

트랜지스터 논리 게이트 애플리케이션

당신이 지금 소유하고 있는 위에서 설명한 디지털 회로로 무엇을 합니까? 기존의 TTL 또는 CMOS 게이트로 달성할 수 있는 모든 것이지만 공급 전압 제한에 대해 걱정할 필요는 없습니다. 다음은 작동 중인 트랜지스터 논리 게이트의 몇 가지 응용 프로그램입니다.

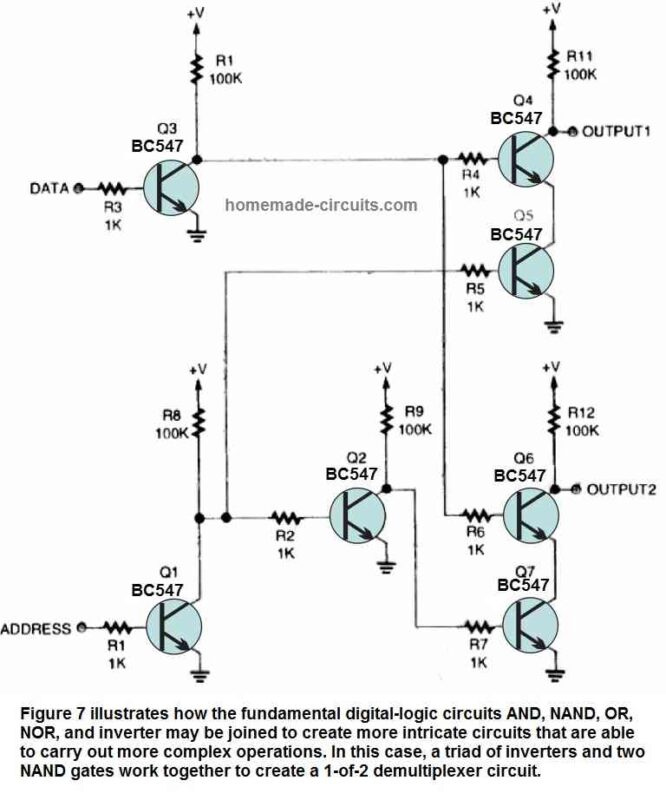

디멀티플렉서 회로

3개의 NOT 게이트와 2개의 NAND 회로가 있는 1/2 디멀티플렉서가 그림 7에 나와 있습니다. 적절한 출력은 1비트 '주소 입력'을 사용하여 선택되며, 이는 OUTPUT1 또는 OUTPUT2일 수 있으며 구동 정보가 적용됩니다. DATA 입력을 사용하는 회로에.

회로는 데이터 속도가 10kHz 미만으로 유지될 때 가장 효과적으로 작동합니다. 회로의 기능은 간단합니다. DATA 입력에는 필요한 신호가 제공되어 Q3을 켜고 Q3의 수집기에서 들어오는 데이터를 반전시킵니다.

Q1의 출력은 ADDRESS 입력이 낮으면 하이로 구동됩니다(접지되거나 신호가 제공되지 않음). Q1의 수집기에서 높은 출력은 두 경로로 나뉩니다. 첫 번째 경로에서 Q1의 출력은 Q5의 베이스(2입력 NAND 게이트의 다리 중 하나)에 공급되어 이를 켜고 Q4와 Q5로 구성된 NAND 게이트를 '활성화'합니다.

두 번째 경로에서 Q1의 높은 출력은 다른 NOT 게이트(Q2)의 입력으로 동시에 공급됩니다. 이중 반전을 거친 후 Q2의 출력은 낮아집니다. 이 로우는 Q7의 베이스(Q6과 Q7로 구성된 두 번째 NAND 게이트의 한 단자)에 공급되어 NAND 회로를 끕니다.

이러한 상황에서 DATA 입력에 적용된 모든 정보 또는 신호는 OUTPUT1에 도달합니다. 또는 ADDRESS 입력에 하이 신호가 주어지면 상황이 반전됩니다. 즉, Q4/Q5 NAND 게이트가 비활성화되고 Q6/Q7 NAND 게이트가 활성화되기 때문에 회로에 제공된 모든 정보는 OUTPUT2에 표시됩니다.

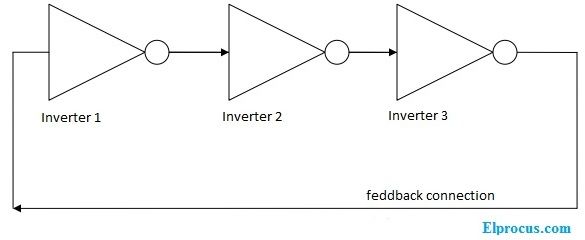

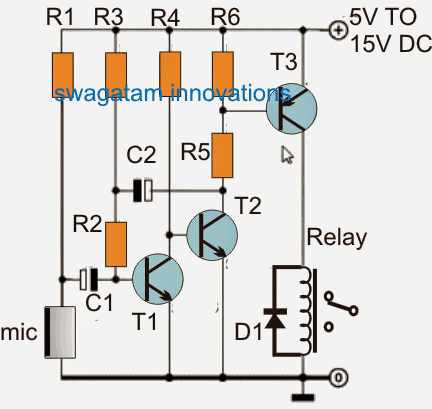

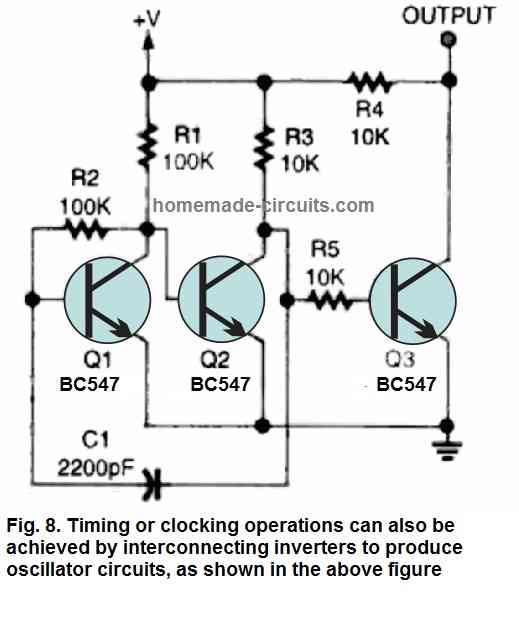

발진기 회로(클록 생성기)

그림 8에 나와 있는 다음 트랜지스터 논리 게이트 애플리케이션은 세 개의 일반 NOT 게이트 인버터(이 중 하나는 피드백 저항 R2를 사용하여 바이어스되며, 아날로그 영역).

출력을 제곱하기 위해 오실레이터 출력을 보완하는 세 번째 NOT 게이트(Q3)가 포함됩니다. C1 값은 회로의 작동 주파수를 변경하기 위해 증가 또는 감소될 수 있습니다. 출력 파형은 표시된 구성 요소 값을 사용하여 1.5V DC에서 V+와 함께 약 7kHz의 주파수를 갖습니다.

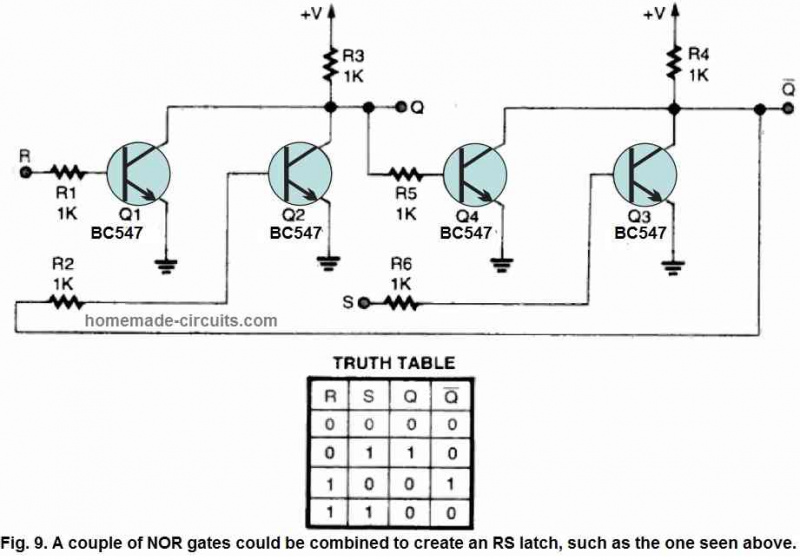

RS 래치 회로

그림 9는 두 개의 NOR 게이트로 구성된 RS 래치인 최종 애플리케이션 회로를 보여줍니다. Q 및 Q 출력에서 건강한 출력 드라이브를 보장하기 위해 저항 R3 및 R4는 1k 옴으로 조정됩니다.

RS 래치의 진리표는 회로도 설계와 함께 표시됩니다. 이것은 개별 트랜지스터를 사용하여 만들 수 있는 몇 가지 신뢰할 수 있는 저전압 디지털 논리 게이트 회로의 몇 가지 예일 뿐입니다.

트랜지스터화된 논리를 사용하는 회로에는 너무 많은 부품이 필요합니다.

이러한 저전압 트랜지스터화된 논리 회로를 모두 사용하여 많은 문제를 해결할 수 있습니다. 그러나 이러한 트랜지스터화된 게이트를 너무 많이 사용하면 새로운 문제가 발생할 수 있습니다.

구축 중인 애플리케이션에 많은 양의 게이트가 포함되어 귀중한 공간을 차지하는 경우 트랜지스터화 및 저항의 수가 상당히 커질 수 있습니다.

트랜지스터 어레이(플라스틱으로 둘러싸인 많은 트랜지스터) 및 SIP(단일 인라인 패키지) 저항을 개별 장치 대신 사용하는 것이 이 문제를 해결하는 한 가지 방법입니다.

위의 접근 방식은 전체 크기의 제품과 동일한 성능을 유지하면서 PCB에서 1톤의 공간을 절약할 수 있습니다. 트랜지스터 어레이는 표면 실장, 14핀 스루홀 및 쿼드 팩 패키지로 제공됩니다.

대부분의 회로에서 트랜지스터 유형을 혼합하는 것은 상당히 수용 가능합니다.

그럼에도 불구하고 실험자는 트랜지스터화된 논리 회로를 구축하기 위해 단일 유형의 트랜지스터로 작업하는 것이 좋습니다(즉, BC547을 사용하여 게이트의 섹션을 만든 다음 나머지 게이트를 만들기 위해 동일한 BJT를 사용하려고 시도함을 의미합니다).

다양한 트랜지스터 변형이 다소 다른 속성을 가질 수 있고 따라서 다르게 동작할 수 있기 때문입니다.

예를 들어, 일부 트랜지스터의 경우 기본 스위치 ON 제한이 다른 것보다 크거나 작을 수 있거나 전체 전류 이득이 약간 더 높거나 낮을 수 있습니다.

반면에 단일 유형의 트랜지스터의 벌크 상자를 구입하는 비용도 더 낮을 수 있습니다. 논리 게이트가 일치하는 트랜지스터를 사용하여 구축되면 회로의 성능이 향상되고 프로젝트 전체가 궁극적으로 더 많은 보상을 받을 것입니다.