현재 우리가 일상에서 사용하는 모든 전기, 전자 장치는 반도체 장치 제조 공정을 활용하여 제조 된 집적 회로로 구성되어 있습니다. 그만큼 전자 회로 다음과 같은 순수한 반도체 재료로 구성된 웨이퍼에 생성됩니다. 실리콘 및 기타 반도체 사진 리소그래피 및 화학 공정을 포함하는 여러 단계의 화합물.

반도체 제조 공정은 1960 년대 초 텍사스에서 시작되어 전 세계로 확장되었습니다.

BiCMOS 기술

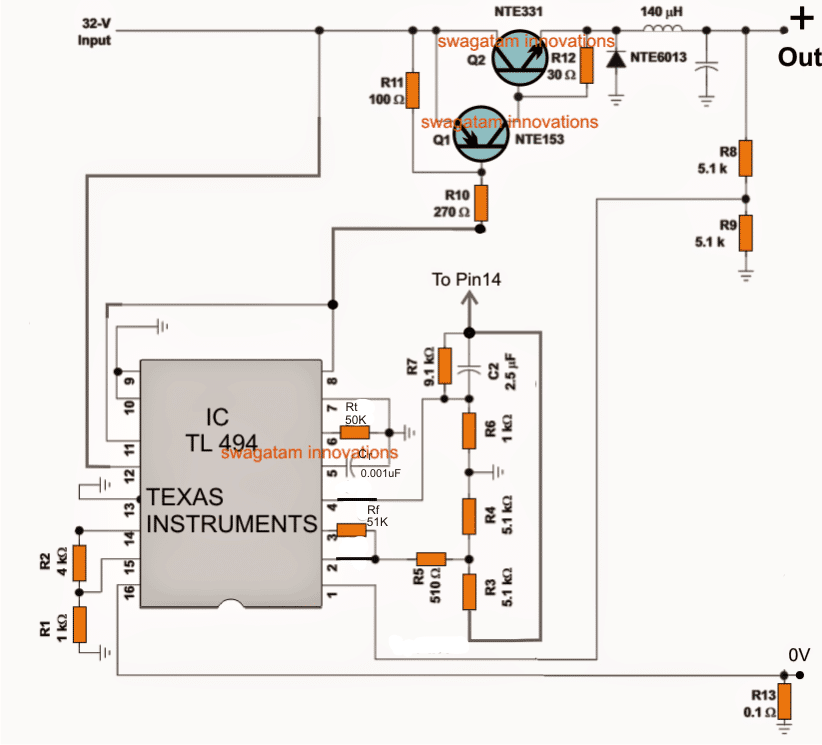

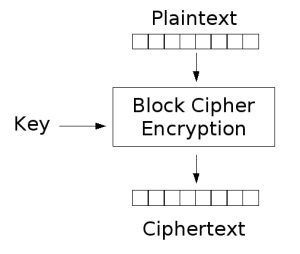

이것은 주요 반도체 기술 중 하나이며 1990 년대 바이폴라 접합 트랜지스터와 CMOS라는 두 가지 개별 기술을 통합 한 고도로 발전된 기술입니다. 트랜지스터 단일 현대 집적 회로에서. 따라서이 기술을 더 잘 활용하기 위해 CMOS 기술과 바이폴라 기술을 간략하게 살펴볼 수 있습니다.

BiCMOS CME8000

표시된 그림은 첫 번째입니다. 아날로그 / 디지털 수신기 IC이며 매우 높은 감도의 BiCMOS 통합 수신기입니다.

CMOS 기술

전자 계산기 제조의 원천으로 시작된 MOS 기술 또는 CSG (Commodore Semiconductor Group)의 보완 제품입니다. 그 후 CMOS 기술이라는 MOS 기술의 보완이 디지털과 같은 집적 회로 개발에 사용됩니다. 논리 회로 와 함께 마이크로 컨트롤러 s 및 마이크로 프로세서. CMOS 기술은 높은 패킹 밀도로 전력 손실이 적고 노이즈 마진이 낮은 이점을 제공합니다.

CMOS CD74HC4067

그림은 디지털 제어 스위치 장치를 제조 할 때 CMOS 기술의 활용을 보여줍니다.

양극성 기술

바이폴라 트랜지스터는 집적 회로의 일부이며 그 동작은 두 가지 유형의 반도체 재료를 기반으로하거나 두 가지 유형의 전하 캐리어 정공과 전자에 의존하며 일반적으로 다음과 같은 두 가지 유형으로 분류됩니다. PNP 및 NPN , 세 단자의 도핑과 극성에 따라 분류됩니다. 그것은 좋은 잡음 성능과 함께 높은 스위칭과 입출력 속도를 제공합니다.

양극성 AM2901CPC

그림은 RISC 프로세서 AM2901CPC에서 바이폴라 기술의 활용을 보여줍니다.

BiCMOS 로직

NMOS 및 PMOS 기술이 매우 낮은 전력 소비 바이폴라 기술과 CMOS 기술에 비해 고속이라는 장점이 서로 융합 된 복잡한 처리 기술입니다 .MOSFET는 높은 입력 임피던스 로직 게이트를 제공하고 바이폴라 트랜지스터는 높은 전류 이득을 제공합니다.

BiCMOS 제작을위한 14 단계

BiCMOS 제작은 BJT와 CMOS 제작 과정을 결합한 것이지만 변형은 기본 구현 일 뿐이며 다음 단계는 BiCMOS 제작 과정을 보여줍니다.

1 단계: P- 기판은 아래 그림과 같이 촬영됩니다.

P 기판

2 단계: p 기판은 산화물 층으로 덮여 있습니다

산화층이있는 P 기판

Step3 : 산화물 층에 작은 구멍이 생깁니다.

산화물 층이 열립니다.

Step4 : N 형 불순물은 개구부를 통해 심하게 도핑됩니다.

N 형 불순물은 개구부를 통해 심하게 도핑됩니다.

Step5 : P – Epitaxy 층은 전체 표면에서 성장합니다.

에피 택시 층은 전체 표면에서 성장합니다

Step6 : 다시 말하지만, 전체 층이 산화물 층으로 덮여 있고이 산화물 층을 통해 두 개의 개구부가 만들어집니다.

산화물 층을 통해 두 개의 구멍이 만들어집니다.

Step7 : 산화막을 통해 형성된 개구부에서 n 형 불순물이 확산되어 n-well을 형성

n 형 불순물이 확산되어 n-well을 형성합니다.

Step8 : 3 개의 활성 장치를 형성하기 위해 산화물 층을 통해 3 개의 개구부가 만들어집니다.

3 개의 활성 장치를 형성하기 위해 산화물 층을 통해 3 개의 개구부가 만들어집니다.

Step9 : NMOS 및 PMOS의 게이트 단자는 Thinox 및 Polysilicon으로 전체 표면을 덮고 패턴 화하여 형성됩니다.

NMOS 및 PMOS의 게이트 단자는 Thinox 및 Polysilicon으로 형성됩니다.

Step10 : P- 불순물은 BJT의베이스 단자를 형성하기 위해 추가되고 유사하게, N- 타입 불순물은 BJT의 에미 터 단자, NMOS의 소스 및 드레인을 형성하기 위해 고농도로 도핑되고 접촉 목적으로 N- 타입 불순물은 N- 웰에 도핑됩니다. 수집기.

P- 불순물이 추가되어 BJT의 기본 단자를 형성합니다.

Step11 : PMOS의 소스 및 드레인 영역을 형성하고 P-베이스 영역에서 접촉하기 위해 P 형 불순물이 많이 도핑됩니다.

P 형 불순물이 많이 도핑되어 PMOS의 소스 및 드레인 영역을 형성합니다.

12 단계 : 그런 다음 전체 표면이 두꺼운 산화물 층으로 덮여 있습니다.

전체 표면이 두꺼운 산화막으로 덮여 있습니다.

Step13 : 두꺼운 산화물 층을 통해 컷이 패턴 화되어 금속 접점을 형성합니다.

컷은 금속 접점을 형성하도록 패턴 화됩니다.

14 단계 : 금속 접점은 산화막에 절단 된 부분을 통해 이루어지며 단자 명은 아래 그림과 같습니다.

금속 접점은 절단을 통해 이루어지며 터미널 이름이 지정됩니다.

BICMOS의 제작은 NMOS, PMOS 및 BJT의 조합으로 위 그림에 나와 있습니다. 제조 공정에서 채널 정지 주입, 두꺼운 층 산화 및 보호 링과 같은 일부 층이 사용됩니다.

제조는 이론적으로 CMOS 및 바이폴라 기술을 모두 포함하기가 어려울 것입니다. 기생 바이폴라 트랜지스터 실수로 생성되는 것은 p-well 및 n-well CMOS를 처리하는 동안 제조 문제입니다. BiCMOS의 제조를 위해 양극 및 CMOS 구성 요소의 미세 조정을 위해 많은 추가 단계가 추가되었습니다. 따라서 총 제작 비용이 증가합니다.

채널 스토퍼는 채널 영역의 확산을 제한하거나 기생 채널의 형성을 피하기 위해 주입 또는 확산 또는 기타 방법을 사용하여 위 그림과 같이 반도체 장치에 주입됩니다.

높은 임피던스 노드가있는 경우 표면 누설 전류를 유발하고 전류 흐름이 제한된 곳에서 전류 흐름을 방지하기 위해 이러한 보호 링이 사용됩니다.

BiCMOS 기술의 장점

- 바이폴라 트랜지스터를 사용하여 입력과 잔량을 실현하는 고 임피던스 CMOS 회로를 사용하여 아날로그 증폭기 설계를 용이하게하고 개선합니다.

- BiCMOS는 본질적으로 온도 및 공정 변동에 강하며 전기 매개 변수의 변동성이 적 으면서 경제적 인 고려 사항 (높은 비율의 프라임 단위)을 제공합니다.

- 요구 사항에 따라 BiCMOS 장치에서 고부하 전류 싱킹 및 소싱을 제공 할 수 있습니다.

- 바이폴라 및 CMOS 기술의 그룹이므로 속도가 중요한 매개 변수 인 경우 BJT를 사용할 수 있고 전력이 중요한 매개 변수 인 경우 MOS를 사용할 수 있으며 감소 된 사이클 시간으로 높은 정전 용량 부하를 구동 할 수 있습니다.

- 바이폴라 기술 만 사용하는 것보다 전력 손실이 적습니다.

- 이 기술은 아날로그 전력 관리 회로 및 BiCMOS 증폭기와 같은 증폭기 회로에서 자주 사용됩니다.

- 입력 / 출력 집약적 인 애플리케이션에 적합하며 유연한 입력 / 출력 (TTL, CMOS 및 ECL)을 제공합니다.

- CMOS 기술 단독에 비해 향상된 속도 성능의 이점이 있습니다.

- 무적을 잡아라.

- 양방향 기능이 있습니다 (요구 사항에 따라 소스와 드레인을 교환 할 수 있음).

BiCMOS 기술의 단점

- 이 기술의 제조 공정은 복잡성을 증가시키는 CMOS 및 양극성 기술로 구성됩니다.

- 제조 공정의 복잡성이 증가함에 따라 제조 비용도 증가합니다.

- 더 많은 장치가 있으므로 리소그래피가 적습니다.

BiCMOS 기술 및 응용

- 고밀도와 속도의 AND 함수로 분석 할 수 있습니다.

- 이 기술은 시장에서 이전 바이폴라, ECL 및 CMOS의 대안으로 사용됩니다.

- 일부 애플리케이션 (전력 예산이 한정된 경우)에서는 BiCMOS 속도 성능이 양극성 성능보다 우수합니다.

- 이 기술은 집약적 인 입 / 출력 애플리케이션에 적합합니다.

- BiCMOS의 애플리케이션은 처음에 기존 CISC 마이크로 프로세서가 아닌 RISC 마이크로 프로세서에있었습니다.

- 이 기술은 주로 메모리와 입력 / 출력과 같은 두 가지 마이크로 프로세서 영역에서 응용 분야에서 탁월합니다.

- 아날로그 및 디지털 시스템에 여러 응용 프로그램이 있으므로 아날로그-디지털 경계에 걸쳐있는 단일 칩이 생성됩니다.

- 그것은 행동 과정과 회로 마진을 넘을 수있는 간격을 넘습니다.

- 높은 임피던스 입력을 제공하므로 샘플 및 홀드 애플리케이션에 사용할 수 있습니다.

- 이것은 가산기, 믹서, ADC 및 DAC와 같은 애플리케이션에서도 사용됩니다.

- 양극성 및 CMOS의 한계를 극복하기 위해 연산 증폭기 BiCMOS 프로세스는 연산 증폭기 설계에 사용됩니다. 연산 증폭기에서는 높은 이득 및 고주파 특성이 필요합니다. 이러한 모든 원하는 특성은 이러한 BiCMOS 증폭기를 사용하여 얻을 수 있습니다.

이 기사에서는 BiCMOS 기술과 그 제조, 장점, 단점 및 애플리케이션에 대해 간략하게 설명합니다. 이 기술에 대한 더 나은 이해를 위해 아래에 의견으로 질문을 게시하십시오.

사진 크레딧 :