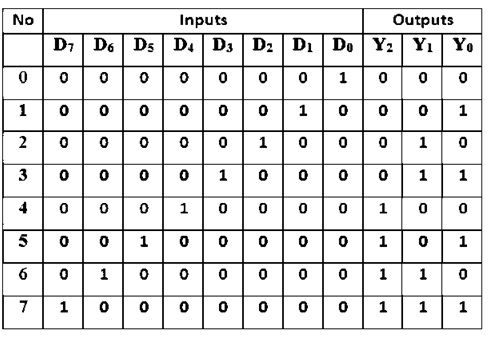

에 디지털 회로 , 이진 가산기 및 감산기는 이진수를 더하고 빼는 데 사용됩니다. 이 회로의 작동은 주로 이진 값에 따라 달라집니다. 여기서 회로의 제어 신호는 이진 값을 보유합니다. 그것은 중 하나입니다 구성 요소 산술 논리 장치의. 이 회로는 반가산기, 전 가산기, 이진 더하기 및 빼기에 대한 필수 정보가 필요합니다. 한 번에 덧셈과 뺄셈을 모두 수행하는 회로를 설계하는 것도 가능합니다. 이 기사에서는 이진 가산기와 이진 빼기의 개요를 설명합니다.

이진 가산기 및 감산기

이진 가산기 및 감산기의 개요는 주로 이진 가산기, 이진 가산기 (반가산기 및 완전 가산기), 병렬 이진 가산기, 이진 감산 회로, 이진 감산기 (반 감산기 및 전체 감산기) 및 병렬 이진 감산기에 대해 설명합니다.

이진 덧셈 회로

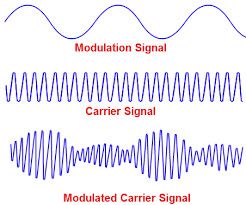

디지털 회로에서 이진 덧셈의 산술 연산은 다음을 사용하여 수행 할 수 있습니다. 논리 게이트 . 이를 위해 2 입력 로직 게이트가 사용되며 OR 게이트와 약간 다릅니다. OR 게이트는 두 개의 정수를 더하고 두 입력이 1 일 때 하나의 출력을 생성합니다. 그러나 OR 게이트는 Exclusive-OR 게이트와 비교할 때 별도의 연산으로 인해 이진 덧셈을 얻지 못합니다. 포괄적 OR 게이트에서는 총합을 생성하기 위해 추가되는 3 개의 o / ps를 포함합니다. 이제이 두 게이트를 서로 비교할 수 있습니다.

이 두 논리 게이트의 주요 차이점은 주로 OR 게이트가 정수 추가를 수행하는 반면 Ex-OR 게이트는 이진 연산을 수행한다는 것입니다.

이진 가산기는 무엇입니까?

이진 가산기는 덧셈과 같은 두 이진수의 산술 연산을 실행하는 데 주로 사용되는 디지털 회로의 한 종류입니다. 이진 가산기는 직렬로 연결하여 전체 가산기 회로로 설계 할 수 있습니다. 첫 번째 완전 가산기의 출력 캐리는 두 번째 완전 가산기의 입력에 연결됩니다. 이 회로는 반 가산기, 완전 가산기 및 병렬 가산기로 분류됩니다.

반가산기

반가산기는 전자 회로 두 개의 이진수를 더하는 데 사용됩니다. 반 가산기는 두 개의 이진수를 더하고 출력과 같은 두 개의 출력을 생성하고 값을 전달합니다. 반가산기의 입력은 A와 B이고 출력은 합과 캐리입니다. 일반적인 표현은 AND 게이트 및 XOR 논리 게이트와 같은 논리 게이트를 사용합니다.

반가산기

완전 가산기

완전 가산기는 세 개의 이진수를 더하는 데 사용되는 전자 회로의 한 종류입니다. 완전 가산기는 세 개의 이진수를 더하고 출력과 같은 두 개의 출력을 생성하고 값을 전달합니다. 반가산기의 입력은 A, B 및 Cin이고 출력은 합계와 Cout입니다. 완전 가산기는 AND 및 XOR 게이트와 같은 논리 게이트가 OR 게이트를 통해 연결된 두 개의 절반 가산기의 조합입니다. 자세한 내용은이 링크를 참조하십시오. 반가산기 및 전 가산기 .

전 가산기

병렬 이진 가산기

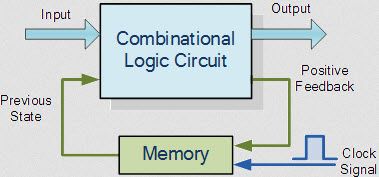

병렬 이진 가산기는 병렬로 연결된 다양한 완전 가산기로 설계된 조합 회로입니다. 병렬 이진 가산기에서 no. 완전 가산기의 수는 주로 아니오에 따라 다릅니다. 거기에 비트의 추가.

병렬 이진 가산기의 설계는 논리 게이트를 사용하여 수행 할 수 있습니다. 논리 회로 내의 관련 모듈은 반 가산기 및 완전 가산기와 같은 두 가산기의 논리 회로처럼 보입니다.

이진 빼기 회로

빼기는 동일한 양을 얻기 위해 한 숫자를 다른 숫자에서 빼는 산술 함수입니다. 다른 숫자를 뺄 숫자를 빼기라고합니다. 마찬가지로, 마이너 드에서 빼는 숫자를 감수라고합니다. 이진 덧셈과 마찬가지로 여기에는 각 감수 비트를 감수 비트에서 뺄 수있는 4 가지 가능한 대체 연산도 포함됩니다.

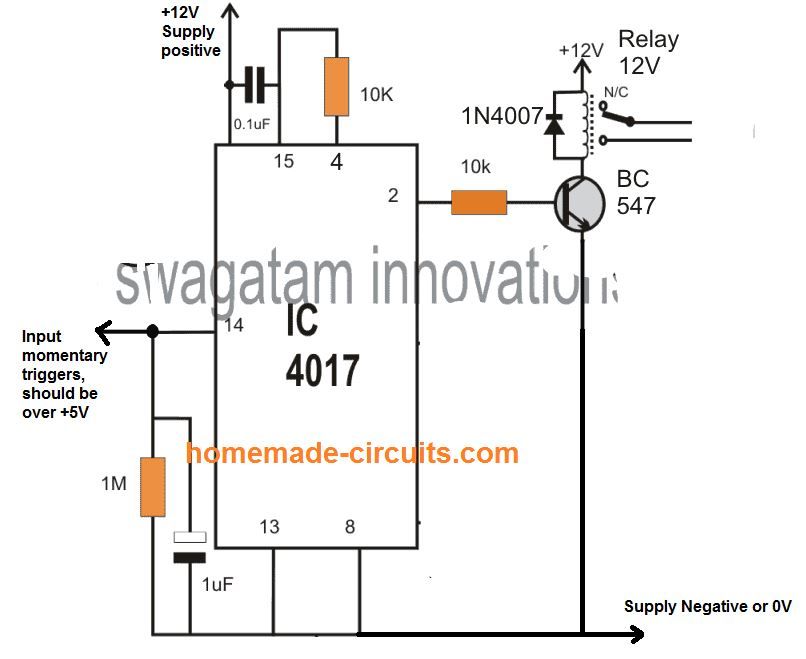

그러나 두 번째 규칙에서는 감수 비트에 비해 마이너 드 비트가 적으므로 뺄셈을 완료하기 위해 1이 대출 중입니다. 가산기 회로와 관련하여 이러한 회로는 반 감산기, 완전 감산기 및 병렬 감산기로 분류됩니다.

반 감산기

반 감산기와 같은 조합 논리 회로]는 두 개의 단일 비트 숫자를 뺄 때 사용됩니다. 여기에는 2 개의 입력과 2 개의 출력이 포함됩니다. 입력은 A, B 인 반면 출력은 차용과 차이입니다. 자세한 내용은이 링크를 참조하십시오. 반 감산기 .

반 감산기

전체 감산기

반 감산기와 같은 조합 논리 회로]는 두 개의 단일 비트 숫자를 뺄 때 사용됩니다. 3 개의 입력과 2 개의 출력을 포함합니다. 입력은 A, B 및 Bin이고 출력은 Borrow & Difference입니다. 전체 감산기에 대한 자세한 내용은이 링크를 참조하십시오. 따라서이 감산기는 하위 단계의 차용을 고려하여 3 비트 감산을 실행하는 기능을 포함합니다. 자세한 내용은이 링크를 참조하십시오. 전체 감산기 .

완전 감산기

병렬 이진 감산기

병렬 이진 감산기는 병렬 내의 동등한 비트 쌍에서 작동하여 길이 내에서 다른 비트보다 우수한 두 이진 숫자의 차이를 찾는 데 사용되는 디지털 회로의 한 종류입니다. 이 감산기의 설계는 감산기의 조합과 감수 보완의 입력을 사용하는 모든 전체 감산기의 조합과 같은 다양한 방법으로 수행 될 수 있습니다.

따라서 이것은 바이너리에 관한 모든 것입니다. 가산기 이진 덧셈 회로, 반 가산기 및 완전 가산기와 같은 이진 가산기, 병렬 이진 가산기, 이진 감산 회로, 절반 감산기 및 전체 감산기와 같은 이진 감산기 및 병렬 이진 감산기를 포함하는 & 감산기. 여기에 질문이 있습니다. Parallel Adder / Subtractor는 무엇입니까?