근본적인 네트워크 정리 네트워크 분석에 사용되는 테브냉(Thévenin's), 중첩(superposition), 노턴(Norton), 치환, 최대 전력 전달, 상호성, 밀먼의 정리 . 모든 정리에는 고유한 적용 영역이 있습니다. 따라서 이러한 정리는 다른 회로에서 반복적으로 사용될 수 있으므로 각 네트워크 정리를 이해하는 것은 매우 중요합니다. 이러한 정리는 주어진 조건에 대해 복잡한 네트워크 회로를 해결하는 데 도움이 됩니다. 이 기사에서는 네트워크 정리의 유형 중 하나에 대해 설명합니다. 대체 정리 – 예.

대체 정리란 무엇입니까?

대체 정리 설명은 다음과 같습니다. 브랜치 전체의 전류 또는 네트워크의 브랜치 양단 전압을 알 때마다 해당 브랜치 전체에 유사한 전압 및 전류를 만드는 다른 요소의 조합에 의해 브랜치가 변경될 수 있습니다. 즉, 다음과 같이 정의할 수 있습니다. 전류뿐만 아니라 열 전압은 분기의 등가를 위해 동일해야 합니다.

대체 정리 개념은 주로 한 요소를 다른 요소로 대체하는 데 의존합니다. 이 정리는 또한 다른 정리를 증명하는 데 매우 유용합니다. 이 정리는 직렬도 병렬도 연결되지 않은 위의 두 소스를 포함하는 정리를 푸는 데 적용할 수 없습니다.

대체 정리의 설명

대체 정리를 푸는 단계는 주로 다음을 포함합니다.

1 단계: 먼저 모든 네트워크 요소의 전압과 전류를 찾아야 합니다. 일반적으로 전압 및 전류는 옴 법칙을 사용하여 계산할 수 있습니다. 키르호프 법칙 KVL 또는 KCL과 같습니다.

2 단계: 전압 소스/저항 및 전류 소스와 같은 다른 요소를 통해 제거하려는 필요한 분기를 선택합니다.

3단계: 전압 및 전류가 변경되지 않아야 하는 경우 대체 요소의 올바른 값을 찾으십시오.

4단계: 단순히 모든 요소의 전류 및 전압을 계산하여 새 회로를 확인하고 원래 네트워크로 평가합니다.

치환 정리 회로도

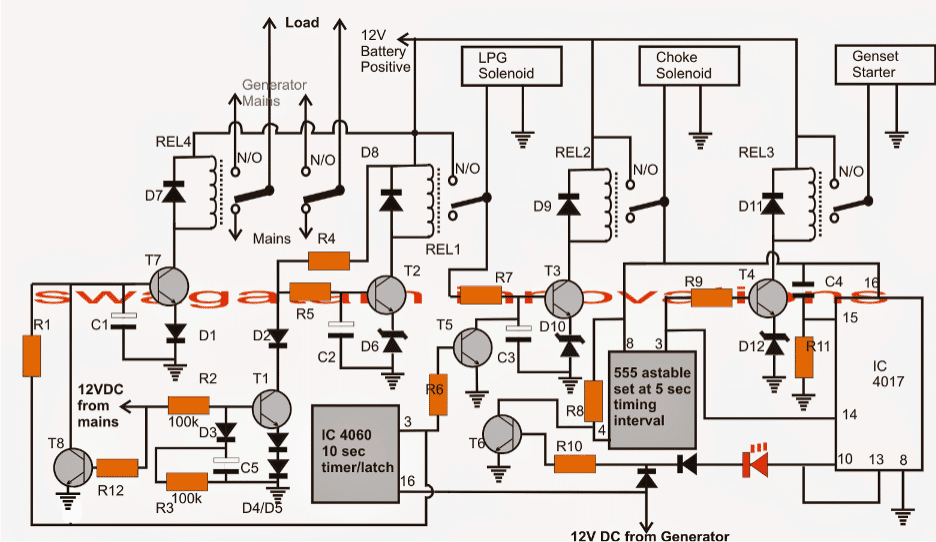

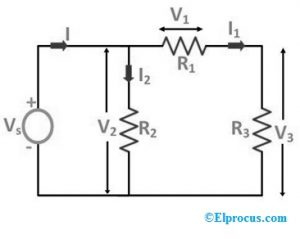

다음 회로도를 사용하여 대체 정리를 쉽게 이해합시다. 우리는 치환 정리가 단일 요소를 다른 동등한 요소로 대체한다는 것을 알고 있습니다. 네트워크 내의 요소가 전류 소스 또는 전압 소스로 교체/대체되는 경우 요소 전체 또는 요소 전체의 전류 및 전압은 이전 네트워크와 같이 변경되지 않은 상태로 유지됩니다.

R1, R2 및 R3과 같은 다양한 저항은 단순히 전압 소스에 연결됩니다. 회로 전체에 흐르는 전류 'I'의 흐름은 I1과 I2로 구분되는데, 회로도와 같이 'I1'은 'R1' 저항 전체에 공급되고 'I2'는 R2 저항 전체에 흐릅니다. 여기에서 저항 R1, R2 및 R3의 전압 강하는 이에 따라 V1, V2 및 V3입니다.

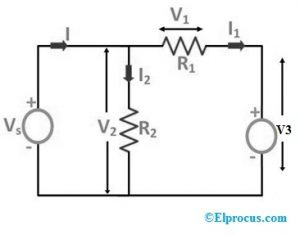

이제 아래 회로도와 같이 'R3' 저항이 'V3' 전압원으로 대체되면:

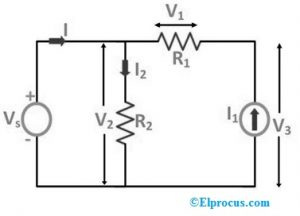

다음 회로도에서 'R3' 저항은 해당 요소 'I1' 전체에 흐르는 전류로 대체됩니다.

위의 두 가지 경우에서 소자를 전류 또는 전압원으로 대체하면 회로의 초기 조건이 변하지 않는다는 것은 저항 양단의 전압 공급 및 저항 전체의 전류 공급은 다른 것으로 교체해도 변하지 않음을 의미합니다. 소스.

예제 문제

대체 정리 예제 문제는 아래에 설명되어 있습니다.

예 1:

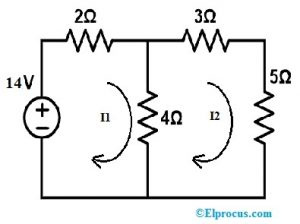

다음 회로를 대입 정리로 풀면 모든 저항기 내의 전압과 전류를 계산할 수 있습니다.

1 단계:

먼저 위의 회로에서 loop1에 KVL을 적용합니다.

14 = 6I1 – 4I2 ….(1)

위의 회로에서 loop2에 KVL을 적용하십시오.

0 = 12I2 – 4I1

12 I2 = 4I1 => I1 = 3I2……….(2)

위의 방정식 1에 이 방정식 2를 대입합니다.

14 = 6(3I2) - 4I2

14 = 18I2 – 4I2 =>14I2 => 1A

I2 = 1A

위의 방정식에서 -(2)

I1 = 3I2

우리는 I2 = 1A라는 것을 알고 있습니다.

I1 = 3A

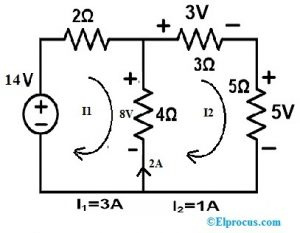

2 단계:

이 단계에서는 단일 루프를 만들기 위해 loop1 분기를 제거해야 합니다.

3단계:

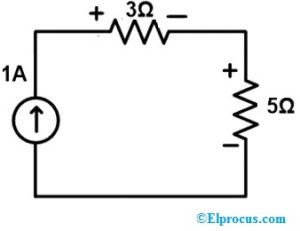

4Ω 저항 대신 전류 소스/전압 소스를 배치할 수 있습니다. 이제 현재 소스를 사용합니다.

회로의 loop2 전체에 흐르는 전류는 1A입니다. 따라서 분기를 1A 전류 소스로 대체합니다. 결과적으로 잔류 회로는 아래와 같습니다.

4단계:

이 단계에서는 모든 요소의 전압 및 전류를 확인해야 합니다. 위의 회로는 단일 루프, 즉 전류 소스를 포함합니다. 따라서 루프 전체에 흐르는 전류 값은 전류 소스 값과 유사합니다.

여기에서 현재 소스 값은 1A입니다. 따라서 3Ω 및 5Ω 저항 분기 전체에 흐르는 전류는 원래 네트워크와 유사한 1A입니다.

를 사용하여 옴 법칙 , 3Ω 저항 양단의 전압 값 찾기

V = IS

V = I x R

V = 1 x 3 => 3V.

마찬가지로 옴 법칙을 사용하여 5Ω 저항의 전압 값을 찾아야 합니다.

V = IS

V = 나 x 5

V = 1 x 5 => 5V.

따라서 전류 및 전압은 원래 네트워크와 유사합니다. 이것이 이 정리가 작동하는 방식입니다.

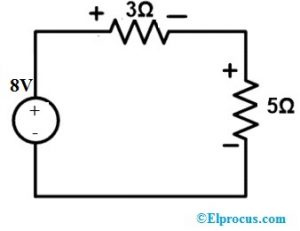

이제 3단계에서 전류원 대신 전압원을 선택하면 이 조건에서 전압원 값은 4Ω 저항 분기 값과 유사합니다.

원래 네트워크 내의 4Ω 저항 분기를 통한 전류 흐름은 다음과 같습니다.

I1 – I2 => 3 – 1 => 2A

옴의 법칙에 따르면;

4Ω 저항의 전압은 V = 2 x 4 = 8V입니다.

따라서 네트워크에서 전압 소스를 8V로 연결해야하며 잔류 회로는 아래 다이어그램과 같습니다.

V= 2 x 4 = 8V

따라서 8V 전압 소스를 네트워크에 연결해야 하며 나머지 회로는 아래 그림과 같습니다.

위의 루프에 KVL을 적용하여 전압 및 전류를 확인합니다.

8 = 3I + 5I => 8I

나 = 1A.

옴 법칙을 사용하여 저항 3Ω의 전압은 다음과 같이 계산할 수 있습니다.

V = 1 × 3 => 3V

마찬가지로 저항 5Ω의 전압은 다음과 같습니다.

V= 1 × 5 => 5V

따라서 전압 및 전류는 원래 네트워크와 대체 후 동일합니다.

예2:

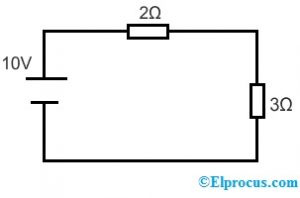

대체 정리를 적용하기 위해 다음 회로를 사용합시다.

전압 분할 눈금자에 따르면 2Ω 및 3Ω 저항의 전압은 다음과 같습니다.

3Ω 저항의 전압은

V = 10×3/3+2 = 6V

2Ω 저항의 전압은

V = 10×2/3+2 = 4V

회로 전체에 흐르는 전류는 I = 10/3+2 = 2A로 계산됩니다.

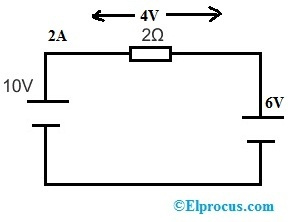

위의 회로에서 3Ω 저항 대신 6V 전압원을 대입하면 회로는 다음과 같이 됩니다.

옴의 법칙에 따라 2Ω 저항에 걸리는 전압과 회로 전체에 흐르는 전류는 다음과 같습니다.

V = 10-6 => 4V

나는 = 10-6/2 = 2A

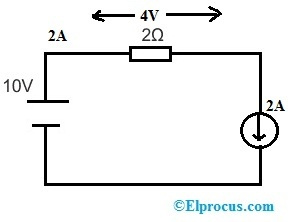

3Ω 저항 대신 2A 전류 소스를 사용하면 회로는 다음과 같이 됩니다.

2Ω 저항 양단의 전압은 V = 10 – 3* 2 => 4V이고 '2A' 전류 소스 양단의 전압은 V = 10 – 4 => 6V입니다. 따라서 2Ω 저항 양단의 전압 및 회로 전체의 전류는 변경되지 않습니다.

장점

그만큼 대체 정리의 장점 다음을 포함합니다.

- 이 정리 개념은 주로 다른 요소에서 단일 요소의 대체에 의존합니다.

- 이 정리는 회로 동작에 대한 직관을 제공하고 다양한 다른 네트워크 정리를 검증하는 데 도움이 됩니다.

- 이 정리를 사용하는 이점은 이 정리가 교차점에 해당하는 X & Y와 같은 변수에 대해 올바른 값을 제공한다는 것입니다.

제한 사항

그만큼 대체 정리의 한계 다음을 포함합니다.

- 이 정리는 직렬/병렬 내에 있지 않은 최소 2개 이상의 소스를 포함하는 네트워크를 해결하는 데 사용할 수 없습니다.

- 이 정리에서는 소자를 교체할 때 회로 동작이 변경되지 않아야 합니다.

애플리케이션

그만큼 대체 정리의 응용 다음을 포함합니다.

- 대체 정리는 수많은 다른 정리를 증명하는 데 사용됩니다.

- 이 정리는 수학의 연립방정식을 푸는 데 도움이 됩니다.

- 이 정리는 회로의 한 요소를 하나 이상의 요소로 대체합니다.

- 이 정리는 종속 소스가 있는 회로를 분석하는 데 사용됩니다.

어느 회로의 대체 정리가 적용되지 않습니까?

위의 두 소스가 병렬 또는 직렬로 연결된 회로에서는 이 대체 정리를 적용할 수 없습니다.

보상 정리를 대체라고 하는 이유는 무엇입니까?

보상 및 대체와 같은 정리는 절차 및 축소 측면에서 동일합니다. 따라서 이 정리는 안테나에 적용할 수 있으며 대체 정리라고도 합니다.

대체 정리를 어떻게 사용합니까?

이 정리는 전체 네트워크의 전압 및 전류에 문제를 일으키지 않고 네트워크 내의 다른 분기로 분기를 대체하여 사용할 수 있습니다. 따라서 이 정리는 선형 및 비선형 회로 모두에서 사용됩니다.

대체 속성이란 무엇입니까?

대체 속성에 따르면 변수 'a'가 다른 변수 'b'와 동일하면 모든 표현식이나 방정식에서 'b' 대신 'a'를 대체할 수 있으며 'b'는 ' a'는 모든 표현식 또는 방정식에서.

따라서 이것은 모든 것에 관한 것입니다. 대체 개요 정리 – 예제가 있는 회로. 여기 당신을 위한 질문이 있습니다. 보상 정리는 무엇입니까?