디지털 하드웨어의 설계 프로세스는 지난 몇 년 동안 크게 변화했습니다. 따라서 PAL 및 PLA를 사용하여 작은 디지털 회로를 구현할 수 있습니다. 각 장치가 사용됩니다. 다양한 회로 구현 특정 칩에서 제공되는 i / ps, o / ps 및 제품 조건의 수보다 더 많이 필요하지 않습니다. 이 칩은 상당히 적당한 크기에 적합하지 않으며 일반적으로 32 개 이하의 상호 입력 및 출력을 지원합니다. 더 많은 입력과 출력이 필요한 이러한 회로를 설계하려면 수많은 PLA / PAL을 사용하거나 더 고급스러운 유형을 사용할 수 있습니다. CPLD (복잡한 프로그래밍 가능 논리 장치)라고하는 칩의 수를 사용할 수 있습니다. CPLD 칩은 회로 블록을 연결하기위한 내부 배선 리소스가있는 단일 칩에 여러 회로 블록을 포함합니다. 각 회로 블록은 PLA 또는 PAL과 유사합니다.

복잡한 프로그래밍 가능 논리 장치 란 무엇입니까?

CPLD의 약어는“Complex programmable logic devices”입니다. 일종의 집적 회로 응용 프로그램 디자이너는 휴대폰과 같은 디지털 하드웨어를 구현하도록 설계합니다. 이는 SPLD (단순 프로그래밍 가능 논리 장치)보다 고의로 더 높은 설계를 처리 할 수 있지만 FPGA보다 적은 논리를 제공합니다 ( 현장 프로그래밍 가능 게이트 어레이 CPLD에는 수많은 논리 블록이 포함되어 있습니다. 각 블록에는 8-16 개의 매크로 셀이 포함됩니다. 모든 로직 블록이 특정 기능을 실행하기 때문에 로직 블록의 모든 매크로 셀이 완전히 연결됩니다. 용도에 따라 이러한 블록은 서로 연결되거나 연결되지 않을 수 있습니다.

복잡한 프로그래밍 가능 논리 장치

대부분의 CPLD (복잡한 프로그래밍 가능 논리 장치)에는 논리 기능과 선택 항목의 합이있는 매크로 셀이 있습니다. FF (플립 플롭) . 칩에 따라 조합 논리 기능은 팬인이 포함 된 4 ~ 16 개의 제품 용어를 지원합니다. CPLD는 시프트 레지스터 및 논리 게이트 측면에서도 다릅니다. 이러한 이유로 FPGA 대신 많은 수의 로직 게이트가있는 CPLD를 사용할 수 있습니다. 또 다른 CPLD 사양은 매크로 셀이 수행 할 수있는 제품 용어의 수를 나타냅니다. 제품 용어는 특정 논리 기능을 실행하는 디지털 신호의 제품입니다.

CPLD는 여러 IC 패키지 형태와 로직 제품군으로 제공됩니다. CPLD는 공급 전압, 작동 전류, 대기 전류 및 전력 손실 측면에서도 다릅니다. 또한 다양한 양의 메모리와 다양한 종류의 메모리 지원을 통해 얻을 수 있습니다. 일반적으로 메모리는 비트 / 메가 비트로 표현됩니다. 메모리 지원은 ROM, RAM 및 듀얼 포트 RAM으로 구성됩니다. 또한 CAM (콘텐츠 주소 지정 가능 메모리), FIFO (선입 선출) 메모리 및 LIFO (후입 선출) 메모리로 구성됩니다.

복잡한 프로그래밍 가능 논리 장치의 아키텍처

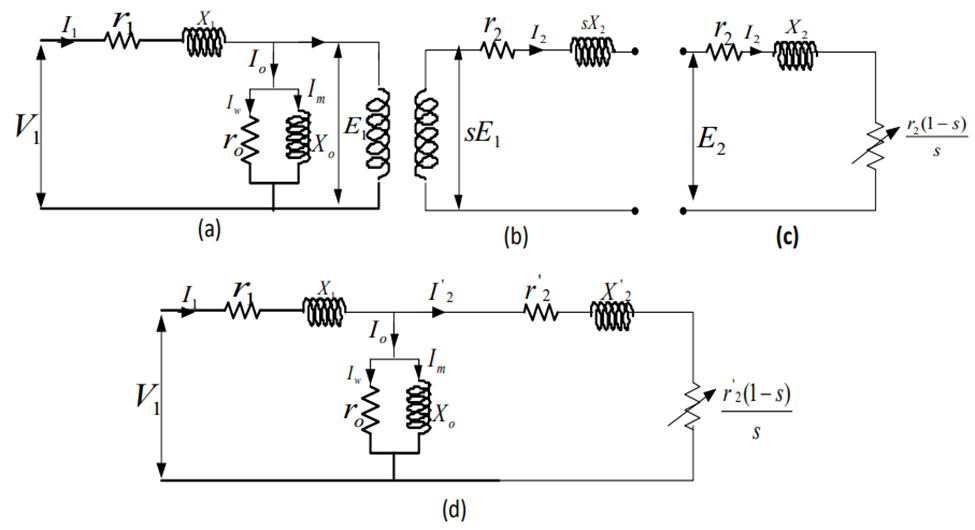

복잡한 프로그래밍 가능 논리 장치는 프로그래밍 가능 FB (기능 블록) 그룹으로 구성됩니다. 이러한 기능 블록의 입력 및 출력은 GIM (전역 상호 연결 매트릭스)에 의해 함께 연결됩니다. 이 상호 연결 매트릭스는 재구성 가능하므로 기능 블록 간의 접점을 수정할 수 있습니다. CPLD를 외부 세계에 통합 할 수있는 몇 가지 입력 및 출력 블록이 있습니다. CPLD의 아키텍처는 다음과 같습니다.

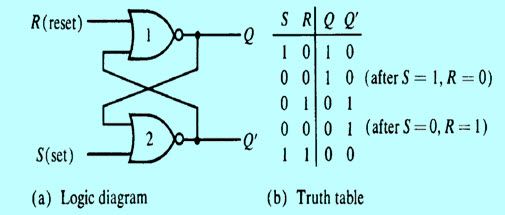

일반적으로 프로그래밍 가능한 FB는 다음과 같습니다. 논리 게이트 배열 , AND 게이트 배열을 프로그래밍 할 수 있고 OR 게이트가 안정적입니다. 그러나 각 제조업체는 기능 블록을 설계하는 방식을 가지고 있습니다. OR 게이트 출력에서 얻은 피드백 신호를 작동하여 나열된 o / p를 찾을 수 있습니다.

CPLD 아키텍처

CPLD 프로그래밍에서는 코드가 시뮬레이션되고 합성되면 먼저 Verilog 또는 VHDL 언어로 설계가 코딩됩니다. 합성 중에 CPLD 모델 (대상 장치)이 직접 선택되고 기술 기반 매핑 넷 목록이 생성됩니다.이 목록은 닫을 수 있습니다. -장소 및 경로 프로세스를 사용하여 정품 CPLD 아키텍처에 적합합니다. 일반적으로 CPLD 회사 소유의 위치 및 경로 소프트웨어에 의해 달성됩니다. 그런 다음 운영자는 몇 가지 확인 프로세스를 수행합니다. 모든 것이 양호하면 CPLD를 사용하고 그렇지 않으면 그는 그것을 재정렬 할 것입니다.

CPLD의 아키텍처 문제

설계에 사용하기 위해 복잡한 프로그래밍 가능 논리 장치를 고려할 때 다음과 같은 아키텍처 문제를 고려할 수 있습니다.

- 프로그래밍 기술

- 기능 블록 기능

- I / O 기능

다른 소매 업체의 CPLD 제품군 중 일부는 다음과 같습니다.

- Altera MAX 7000 및 MAX 9000 제품군

- Atmel ATF 및 ATV 제품군

- Lattice isp LSI 제품군

- Lattice (Vantis) MACH 제품군

- Xilinx XC9500 제품군

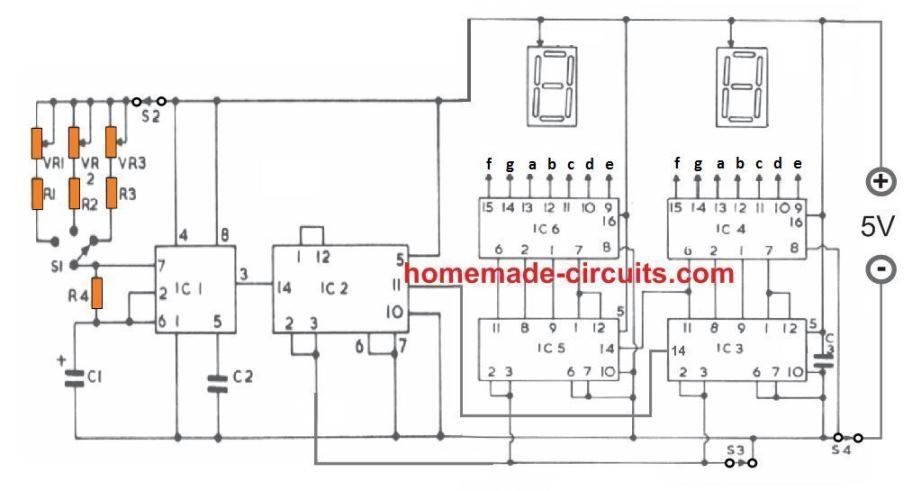

CPLD의 가족

CPLD의 응용

CPLD의 응용 프로그램은 다음과 같습니다.

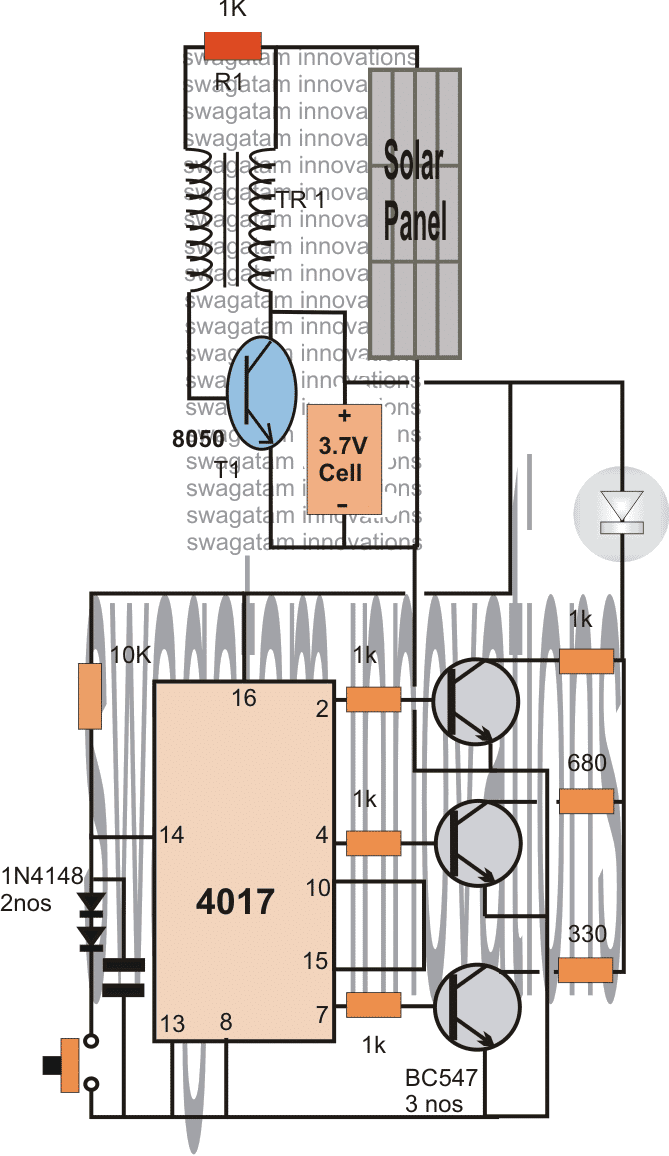

- 복잡한 프로그래밍 가능 논리 장치는 고성능의 중요한 제어 애플리케이션에 이상적입니다.

- CPLD는 디지털 설계에서 부트 로더의 기능을 수행하는 데 사용할 수 있습니다.

- CPLD는 비 휘발성 메모리에서 필드 프로그래밍 가능 게이트 어레이의 구성 데이터를로드하는 데 사용됩니다.

- 일반적으로 주소 디코딩과 같은 소규모 설계 응용 프로그램에 사용됩니다.

- CPLD는 크기가 작고 전력 사용량이 적기 때문에 비용에 민감한 배터리로 작동하는 휴대용 장치와 같은 많은 애플리케이션에서 자주 사용됩니다.

따라서 이것은 복잡한 프로그래밍 가능 논리 장치 아키텍처 및 응용 프로그램에 관한 것입니다. 이 개념을 더 잘 이해 하셨기를 바랍니다. 또한이 개념 또는 전기 및 전자 프로젝트 구현 , 아래 댓글 섹션에 댓글을 달아 소중한 제안을 보내주세요. CPLD와 FPGA의 차이점은 무엇입니까?

사진 크레딧 :